iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

# SQ7615 中文产品规格书 V1.9

Page: 1/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

No.: TDDS01-S7615-CN

## Name: SQ7615 中文产品规格书

## 目录

Version: V1.9

| 1.产品简介              | 10 |

|---------------------|----|

| 1.1 功能特性            | 10 |

| 1.2 重点说明            | 11 |

| 1.3 系统模块图           | 13 |

| 1.4 引脚配置/说明         | 14 |

| 1.5 I/O 线路图         | 22 |

| 2.电气特性              | 25 |

| 2.1 极限参数            | 25 |

| 2.2 工作条件            | 26 |

| 2.2.1 工作条件          | 26 |

| 2.2.2 时钟源           | 26 |

| 2.2.3 I/O 特性        | 27 |

| 2.3 直流(DC)特性        | 28 |

| 2.4 上电复位电气特性        | 30 |

| 2.5 BROR 电气特性       | 31 |

| 2.6 LVD 电气特性        | 32 |

| 2.7 ADC 电气特性        | 33 |

| 2.8 FLASH 电气特性      | 34 |

| 3. 中央处理器(CPU)       | 35 |

| 3.1 符号对照            | 36 |

| 3.2 核心寄存器           | 38 |

| 3.2.1 8 位通用寄存器      | 38 |

| 3.2.2 16 位通用寄存器     | 39 |

| 3.2.3 程序状态字         | 40 |

| 3.2.4 堆栈指针(SP)      | 41 |

| 3.2.5 程序计数器(PC)     | 41 |

| 3.3 寻址模式            | 42 |

| 3.3.1 寄存器间接寻址       | 42 |

| 3.3.2 直接寻址          | 43 |

| 3.3.3 寄存器寻址(r 或 rr) | 43 |

|                     |    |

No.: TDDS01-S7615-CN

## iMQ Technology Inc.

| <u> </u>                | <u> </u> |

|-------------------------|----------|

| 3.3.4 立即寻址(n 或 mn)      | 43       |

| 3.3.5.相对寻址              | 44       |

| 3.3.6 绝对寻址              | 44       |

| 3.3.7 矢量寻址              | 44       |

| 3.3.8 直接位尋址             | 44       |

| 3.3.9 寄存器间接位寻址          | 45       |

| 3.4 指令流水線               | 46       |

| 3.4.1 寄存器对寄存器运行         | 46       |

| 3.4.2 寄存器对存储器运行         | 46       |

| 3.4.3 存储器对寄存器运行         | 47       |

| 3.4.4 存储器对存储器运行         | 47       |

| 3.4.5 跳转                | 48       |

| 3.4.6 子过程调用及返回          | 49       |

| 3.4.7 软件中断(SWI)         | 50       |

| 3.5 指令集总结               | 51       |

| 3.5.1 数据传送及交换指令         | 51       |

| 3.5.2 算数逻辑单元(ALU)指令     | 52       |

| 3.5.3 位移/旋转及半字节操作指令     | 55       |

| 3.5.4 位及标志操作指令          | 56       |

| 3.5.5 跳转指令              | 58       |

| 3.5.6 呼叫、返回、软件中断以及无操作指令 | 59       |

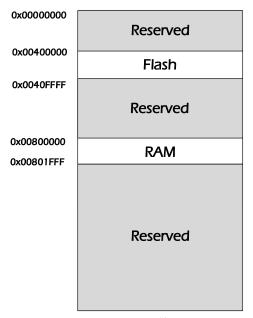

| 4.寻址区域                  | 60       |

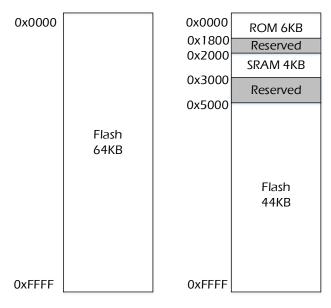

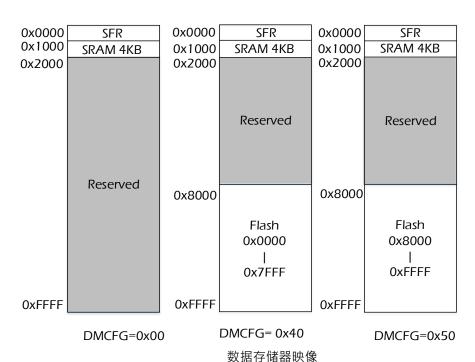

| 4.1 系统存储器架构             | 61       |

| 4.1.1 系统控制寄存器           | 63       |

| 4.1.2 系統外围线路及控制寄存器      | 66       |

| 4.2 外围存储器               | 70       |

| 4.2.1 外围存储器区域 1         | 70       |

| 5.系统运行                  | 74       |

| 5.1 工作模式                | 74       |

| 5.1.1 一般模式              | 76       |

| 5.1.2 睡眠模式              | 76       |

Name: SQ7615 中文产品规格书

No.: TDDS01-S7615-CN

## iMQ Technology Inc.

|                                | •   |

|--------------------------------|-----|

| 5.1.3 深眠模式                     | 76  |

| 5.1.4 低功耗模式                    | 77  |

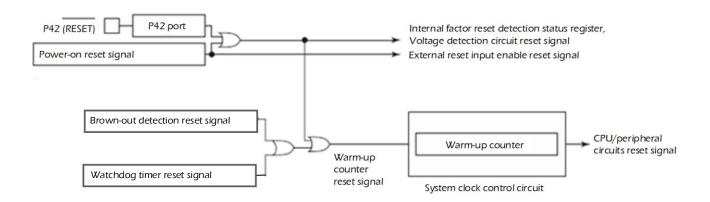

| 5.2 复位控制线路                     | 78  |

| 5.2.1 复位架构                     | 78  |

| 5.2.2 复位控制                     | 79  |

| 5.2.3 复位功能                     | 81  |

| 5.2.4 装置初始化                    | 82  |

| 5.2.5 复位信号产生因素                 | 84  |

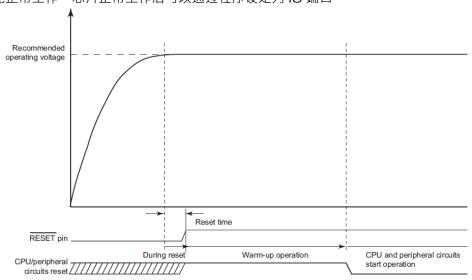

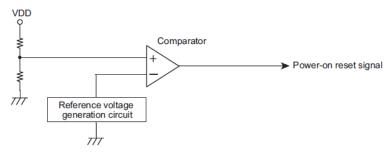

| 5.3 上电复位线路                     | 87  |

| 5.3.1 上电复位架构                   | 87  |

| 5.3.2 上电复位功能                   | 87  |

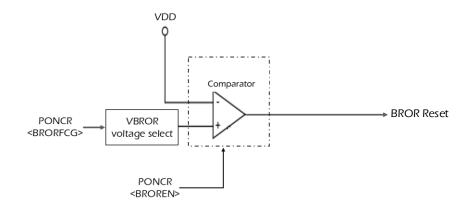

| 5.4 掉电复位 (BROR)                | 88  |

| 5.4.1 掉电复位架构                   | 88  |

| 5.4.2 掉电复位功能                   | 88  |

| 5.4.3 掉电复位控制                   | 89  |

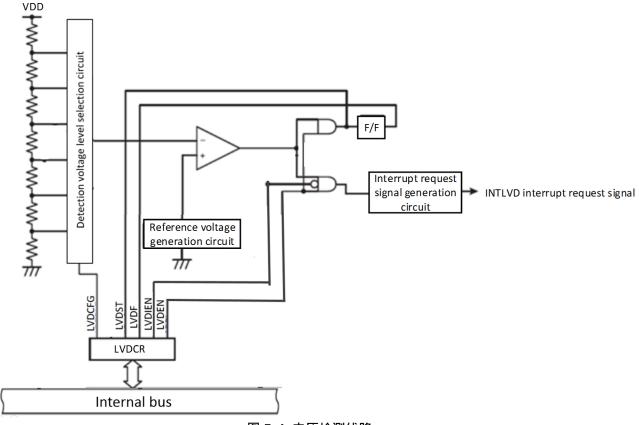

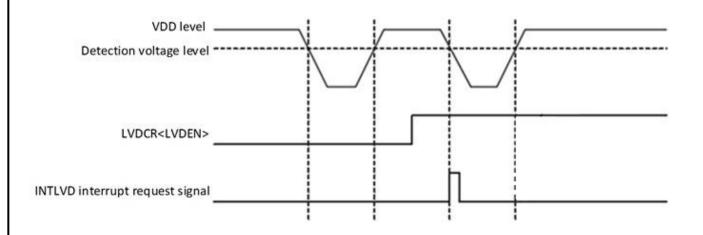

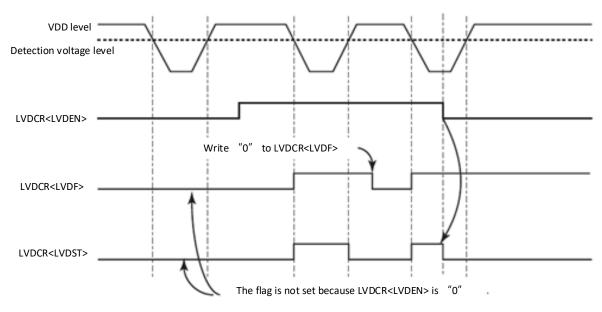

| 5.5 电压检测线路                     | 90  |

| 5.5.1 电压检测架构                   | 90  |

| 5.5.2 电压检测控制                   | 91  |

| 5.5.3 电压检测功能                   | 92  |

| 5.5.4 电压检测寄存器设定                | 94  |

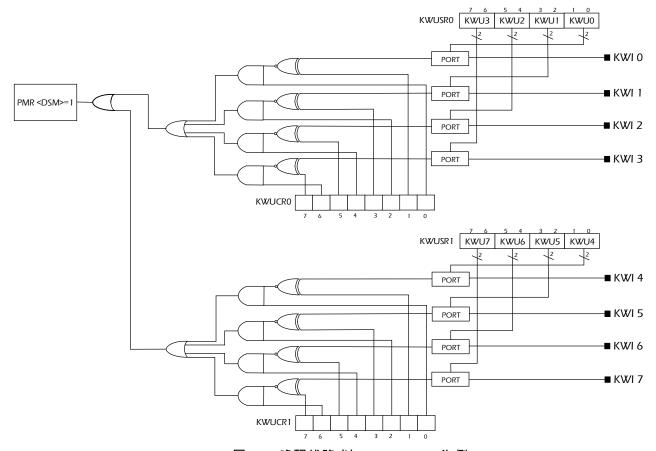

| 5.6 唤醒 KWU                     | 95  |

| 5.6.1 唤醒 KWU 架构                | 95  |

| 5.6.2 唤醒 KWU 控制寄存器             | 96  |

| 5.6.3 KWU 控制寄存器                | 99  |

| 5.7 中断                         | 100 |

| 5.7.1 非屏蔽中断                    | 100 |

| 5.7.2 屏蔽中断                     | 100 |

| 5.7.3 中断列表                     | 101 |

| 5.7.4 中断控制器 (INTC)             | 104 |

| 5.7.5 中断标帜寄存器 (IFRx, x=0~11)   |     |

| 5.7.6 中断允许寄存器 x (IERx, x=0~11) |     |

|                                |     |

Name: SQ7615 中文产品规格书

No.: TDDS01-S7615-CN

## iMQ Technology Inc.

| 5.7.7 中断优先级变更          | 108 |

|------------------------|-----|

| 5.7.8 中断处理             | 109 |

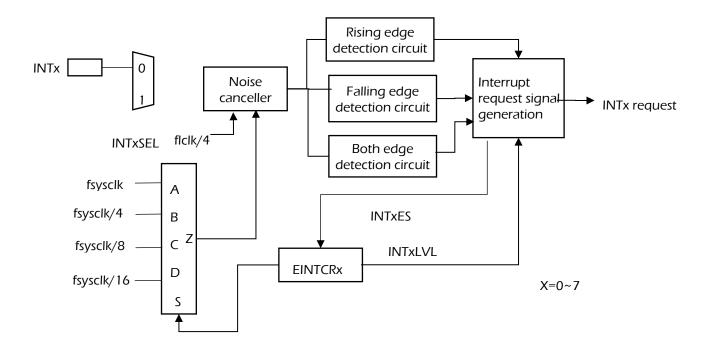

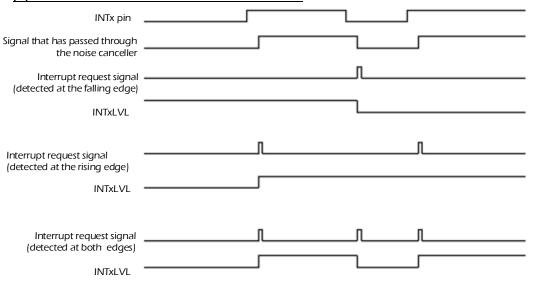

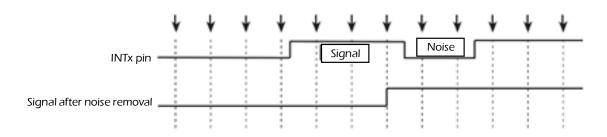

| 5.8 外部中断控制线路           | 110 |

| 5.8.1 外部中断架构           | 110 |

| 5.8.2 外部中断控制           | 111 |

| 5.8.3 外部中断功能           | 113 |

| 5.9 系统供电监控             | 116 |

| 5.9.1 系统供电监控控制寄存器      | 116 |

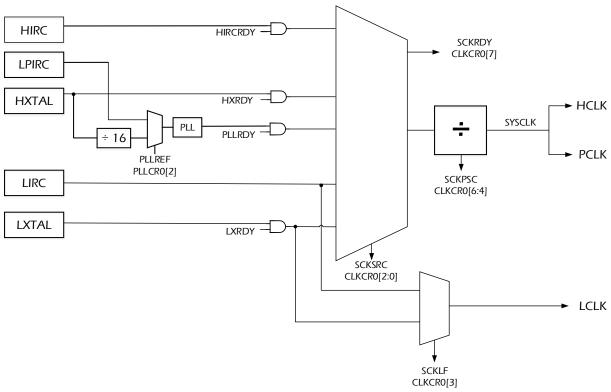

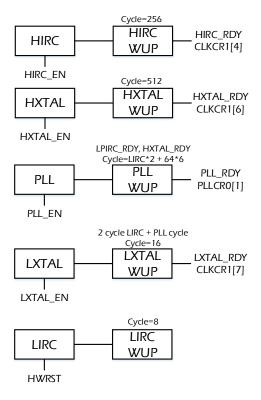

| 6.系统时钟控制器              | 118 |

| 6.1 时钟源                | 118 |

| 6.2 时钟切换               | 119 |

| 6.3 时钟监控               | 120 |

| 6.4 时钟控制寄存器            | 121 |

| 6.5 系统及外围电路时钟          | 126 |

| 6.5.1 功能性门控时钟          | 126 |

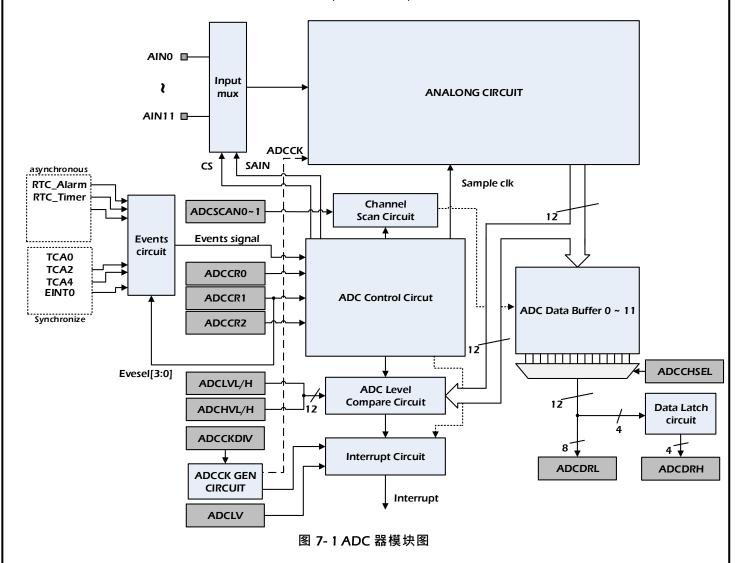

| 7. 12 位 ADC            | 131 |

| 7.1 功能叙述               | 132 |

| 7.1.1 ADC 控制寄存器        | 132 |

| 7.1.2 数据缓存器            | 133 |

| 7.1.3 多重信道扫描           | 133 |

| 7.1.4 ADC 时钟源选择        | 133 |

| 7.1.5 ADC 参考           | 133 |

| 7.1.6 ADC 事件源          | 133 |

| 7.1.7 ADC 阶层比较         | 134 |

| 7.1.8 中断产生             | 134 |

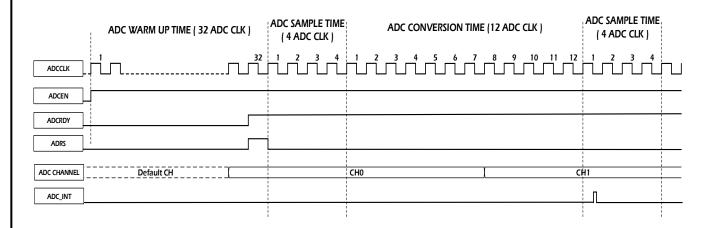

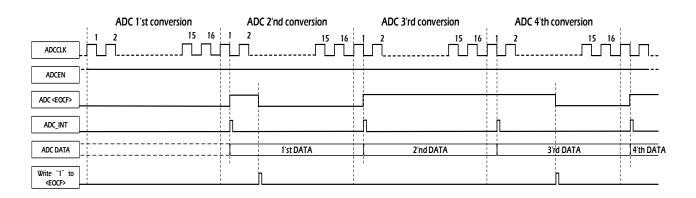

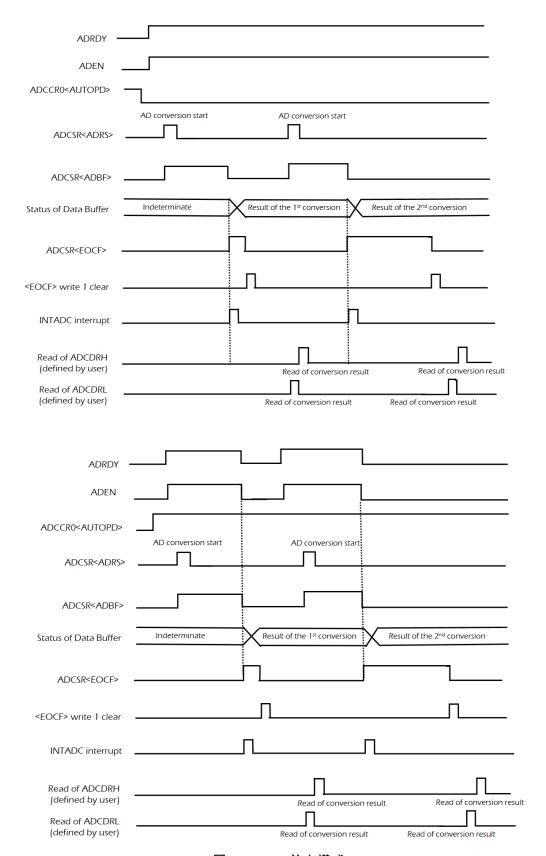

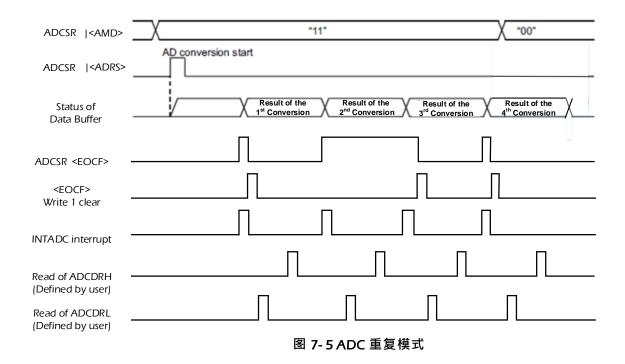

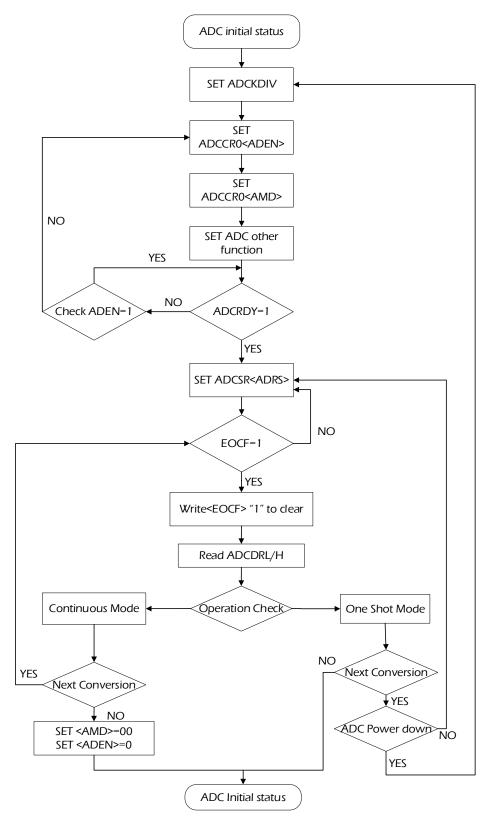

| 7.1.9 ADC 工作模式         | 135 |

| 7.1.10 停止 AD 工作        | 138 |

| 7.1.11 ADC 工作流程        | 139 |

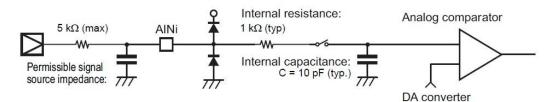

| 7.2 注意事项               | 141 |

| 7.2.1 模拟信号输入引脚电压范围     | 141 |

| 7.2.2 模拟信号输入引脚作 I/O 埠用 | 141 |

|                        |     |

Name: SQ7615 中文产品规格书

## iMQ Technology Inc.

| No.: TDDS01-S7615-CN | Name: SQ7615 中文产品规格书 | Version: V1.9 |

|----------------------|----------------------|---------------|

| 7.2.3 噪声抑制           |                      | 141           |

|                      |                      |               |

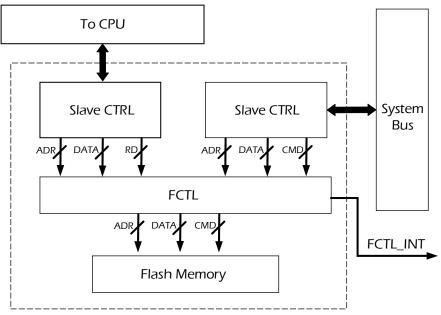

| 8. FLASH 存储控制器(FMC)  |                      | 151           |

| 8.1 功能叙述             |                      | 151           |

| 8.2 FLASH 储存控制寄存器    |                      | 152           |

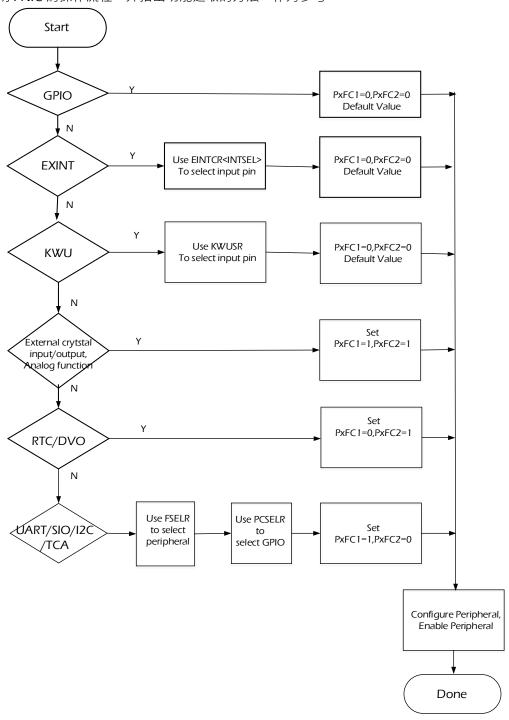

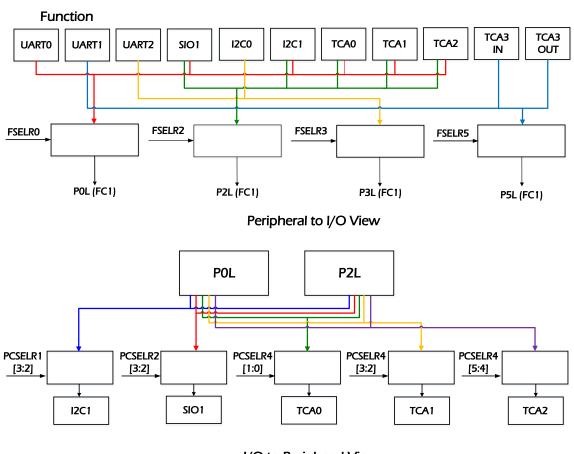

| 9. 通用 I/O            |                      | 156           |

| 9.1 I/O 埠控制寄存器       |                      | 158           |

| 9.2 I/O 埠寄存器         |                      | 159           |

| 9.2.1 P0 端口寄存器       |                      | 159           |

| 9.2.2 P1 端口寄存器       |                      | 162           |

| 9.2.3 P2 端口寄存器       |                      | 164           |

| 9.2.4 P3 端口寄存器       |                      | 166           |

| 9.2.5 P4 端口寄存器       |                      | 168           |

| 9.2.6 P5 端口寄存器       |                      | 170           |

| 10 乘法器(MAC)          |                      | 172           |

| 10.1 工作模式            |                      | 172           |

| 10.2 乘法器寄存器          |                      | 175           |

| 11 外围网络互连控制(PNIC)    |                      | 180           |

| 11.1 功能叙述            |                      | 180           |

| 11.2 PNIC 操作流程       |                      | 181           |

| 11.3 PNIC 控制寄存器      |                      | 182           |

| 11.4 PNIC 范例架构图      |                      | 193           |

| 12.定时器/计数器           |                      | 194           |

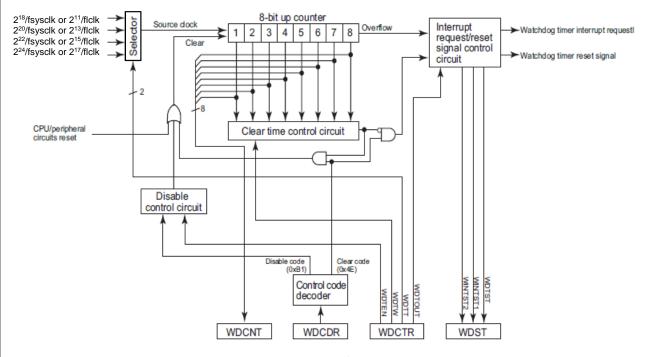

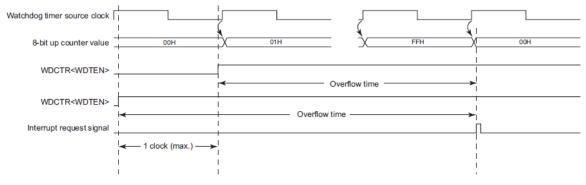

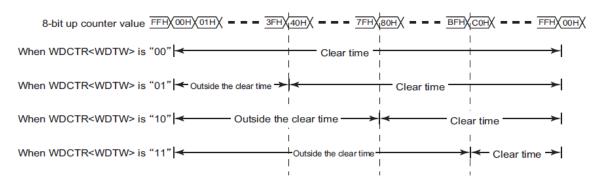

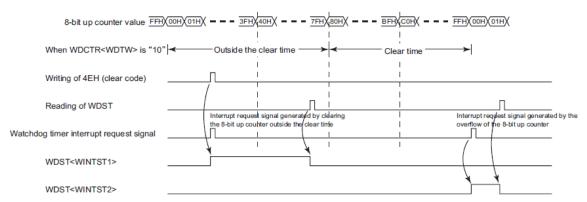

| 12.1 看门狗定时器(WDT)     |                      | 194           |

| 12.1.1 看门狗定时器架       | 构                    | 194           |

| 12.1.2 看门狗定时器控       | 制                    | 195           |

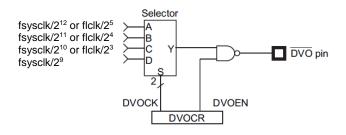

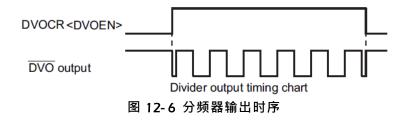

| 12.2 分频器输出(DVO)      |                      | 202           |

| 12.2.1 分频器输出架构。      |                      | 202           |

| 12.2.2 分频器输出控制       |                      | 202           |

| 13.2.3 分频器输出功能       |                      | 203           |

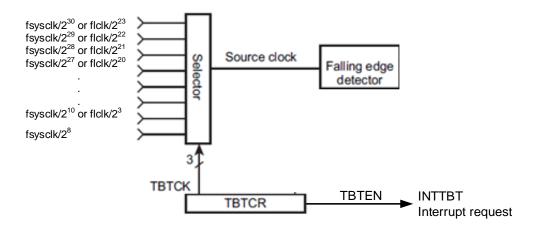

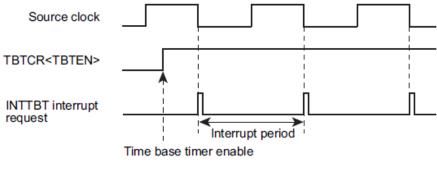

| 12.3 时基定时器(TBT)      |                      | 204           |

No.: TDDS01-S7615-CN

## iMQ Technology Inc.

| 12.3.1 时基定时器架构                         | 204 |

|----------------------------------------|-----|

| 12.3.2 时基定时器控制                         | 205 |

| 12.3.3 时基定时器功能                         | 206 |

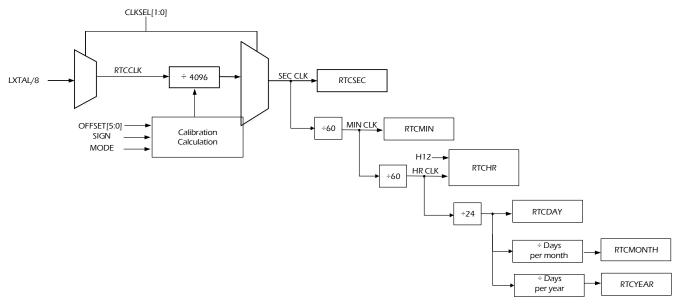

| 12.4 实时时钟(RTC)                         | 208 |

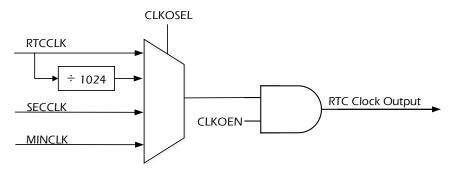

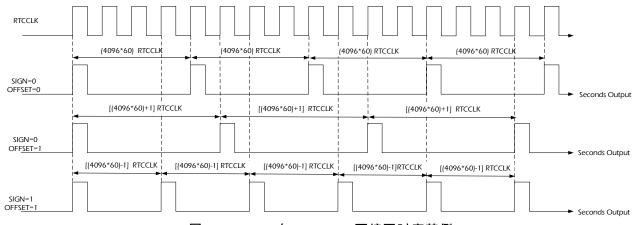

| 12.4.1 功能叙述                            | 208 |

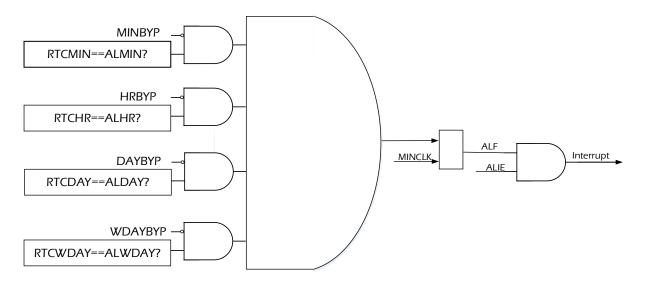

| 12.4.2 RTC 工作模式                        | 208 |

| 12.4.3 实时时钟寄存器                         | 212 |

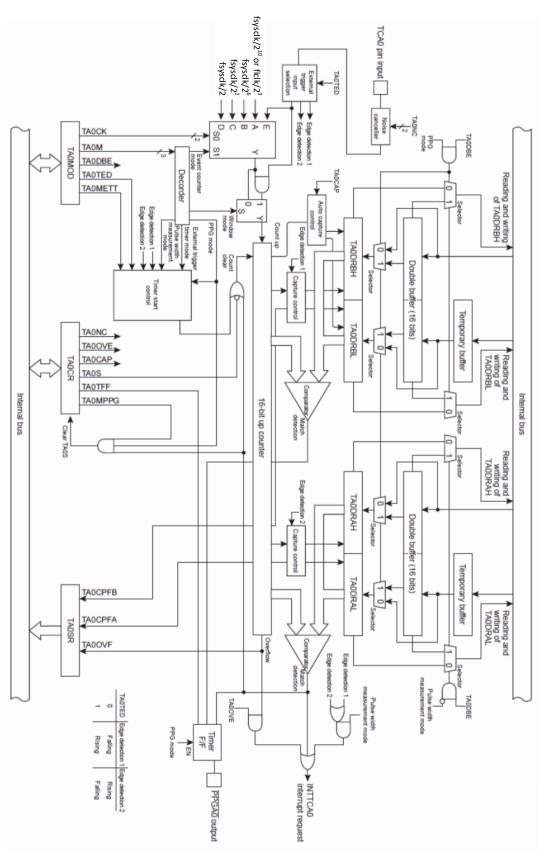

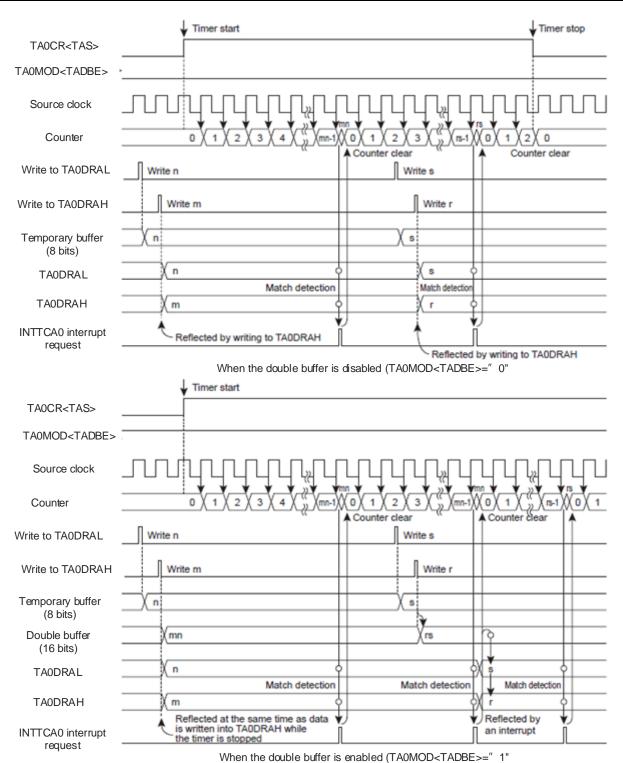

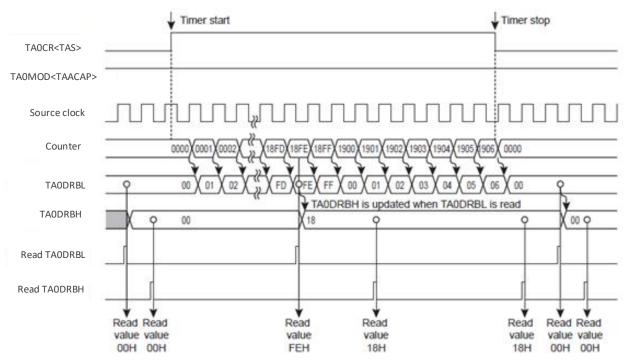

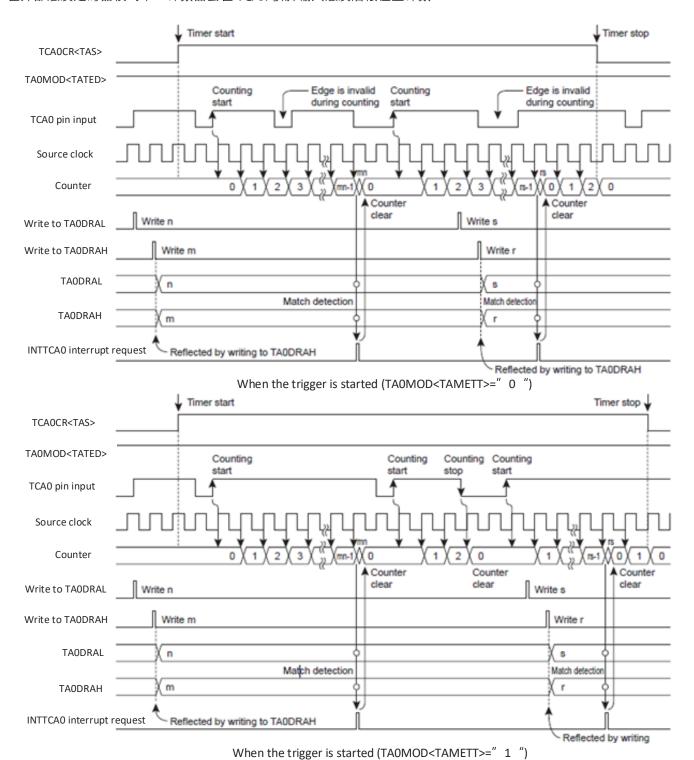

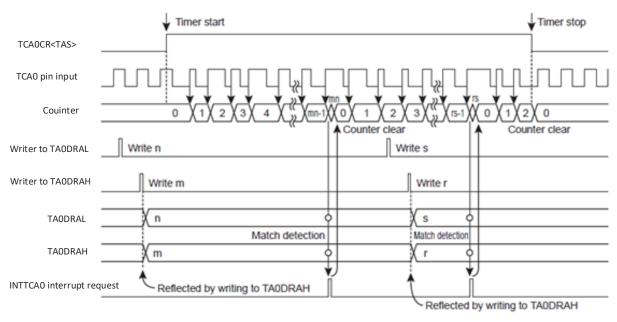

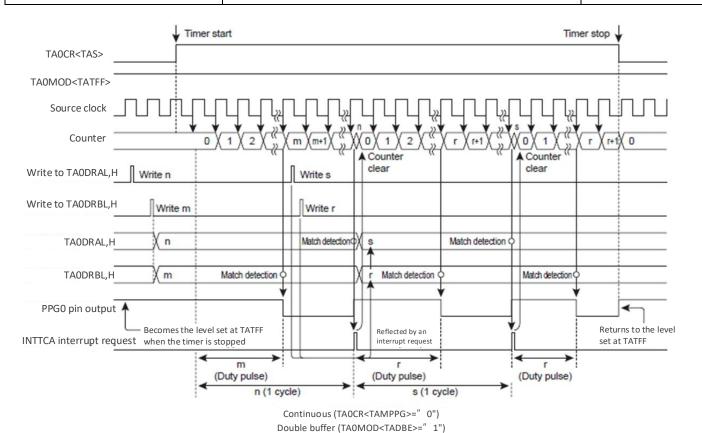

| 12.5 16 位定时器                           | 222 |

| 12.5.1 16 位定时器计数器控制                    | 224 |

| 12.5.2 低耗电功能                           | 229 |

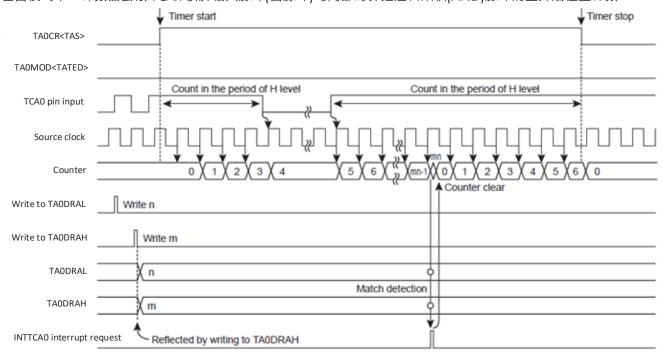

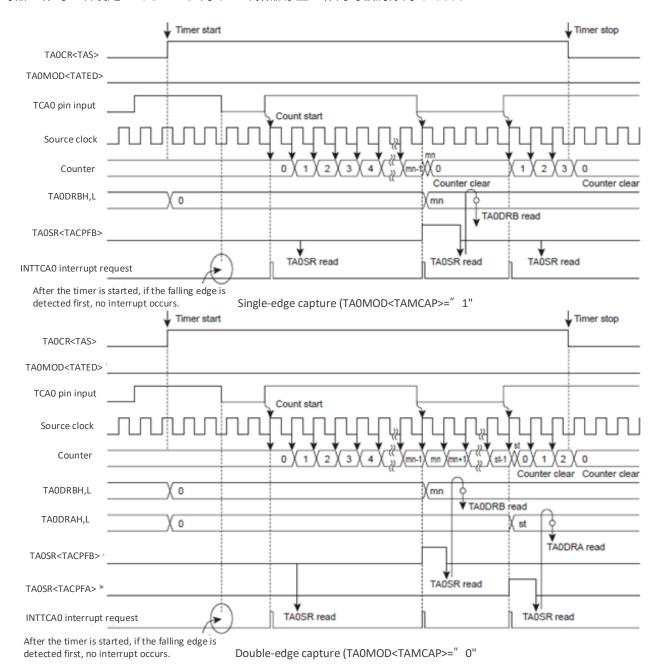

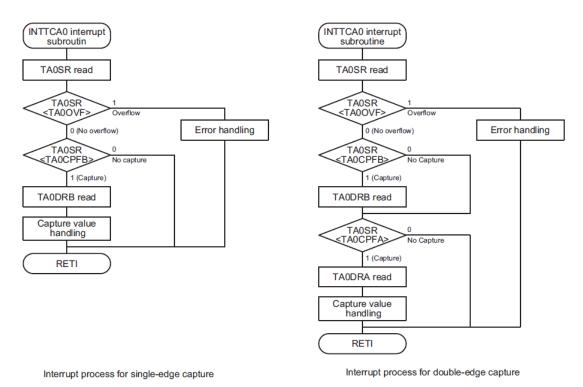

| 12.5.3 定时器功能                           | 230 |

| 12.5.4 噪声抑制                            | 246 |

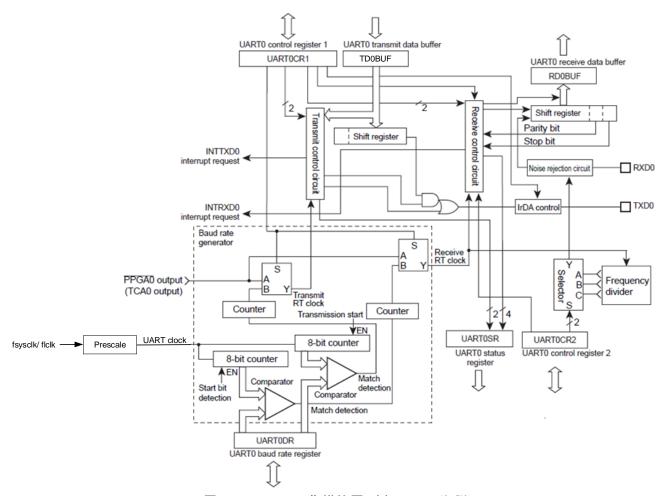

| 13.通用异步收发器 (UART)                      | 247 |

| 13.1 UART 架构                           | 248 |

| 13.2 UART 控制                           | 252 |

| 13.3 防止 UARTxCR1 与 UARTxCR2 寄存器改变的保护机制 | 252 |

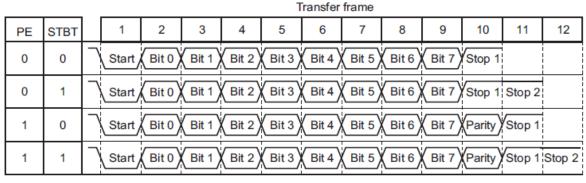

| 13.4 收发数据格式                            | 253 |

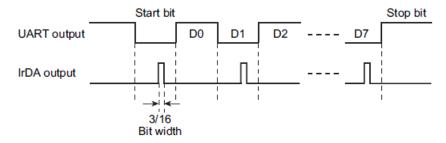

| 13.5 红外线数据收发模式                         | 254 |

| 13.6 收发波特率 (BAUD RATE)                 | 255 |

| 13.6.1 收发波特率计算方法                       | 257 |

| 13.6.2 如何以 TCA 作为 UART 的时钟源            | 259 |

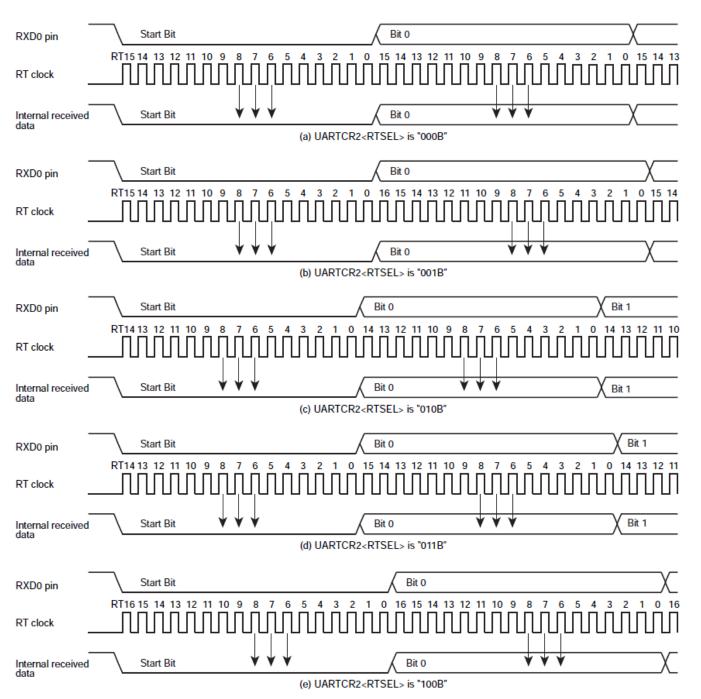

| 13.7 数据取样方法                            | 261 |

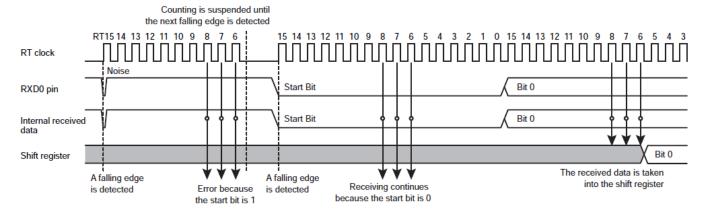

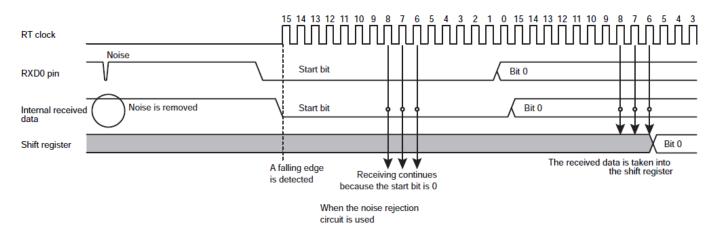

| 13.8 接收数据的噪声抑止                         | 263 |

| 13.9 发送/接收工作                           | 264 |

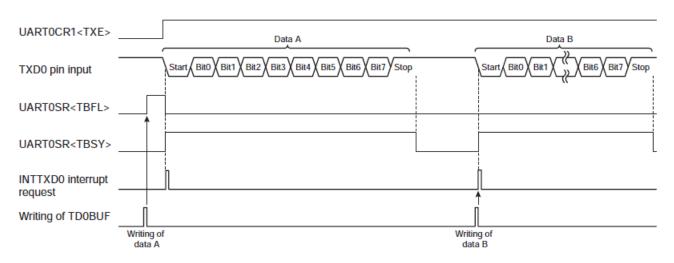

| 13.9.1 资料发送工作                          |     |

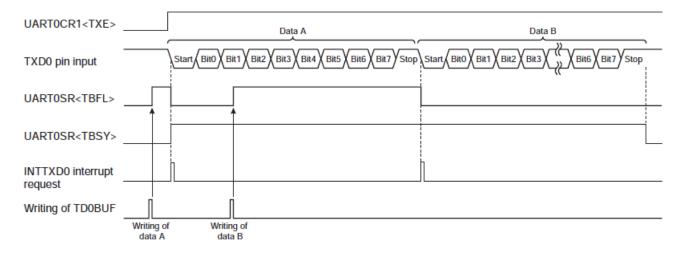

| 13.9.2 数据接收工作                          | 264 |

| 13.10 状态标帜                             | 265 |

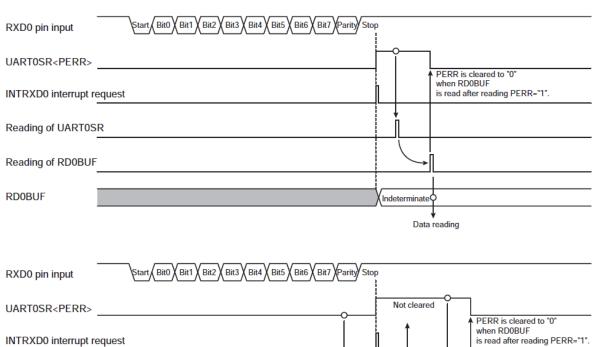

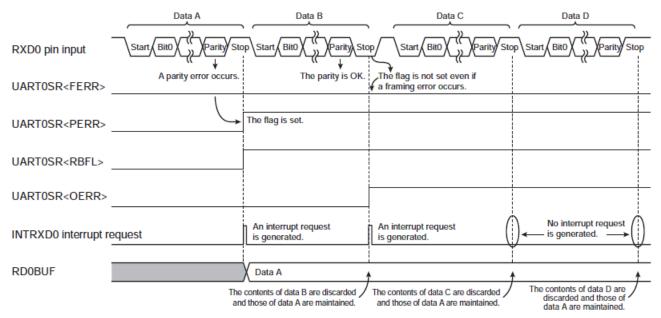

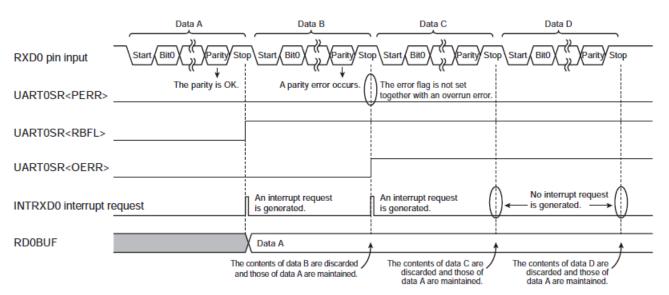

| 13.10.1 同位错误标帜                         | 265 |

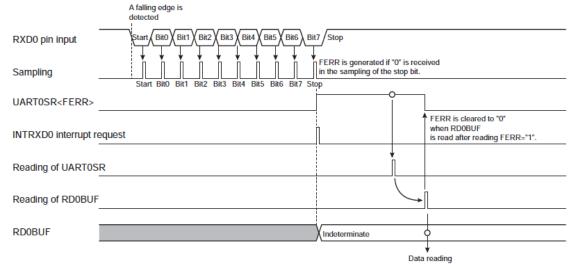

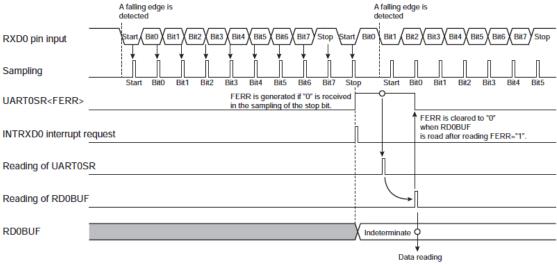

| 13.10.2 数据框错误标帜                        | 266 |

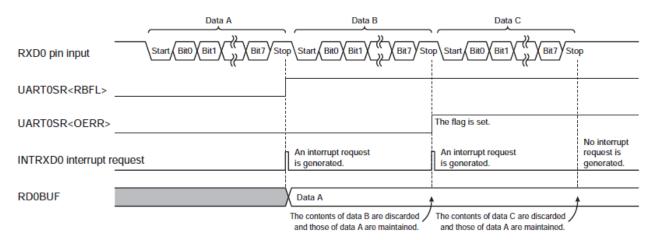

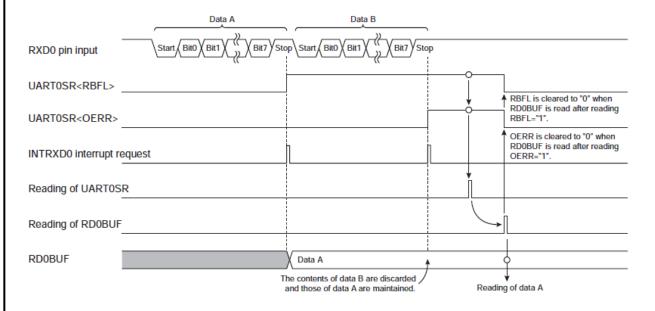

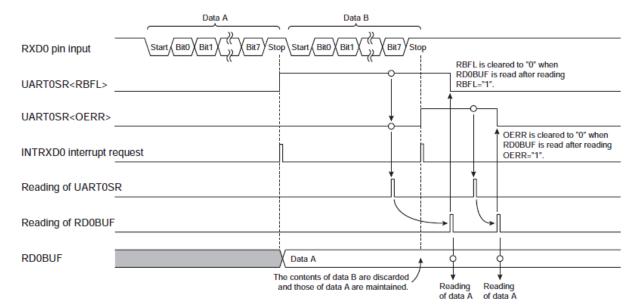

| 13.10.3 溢出错误标帜                         | 267 |

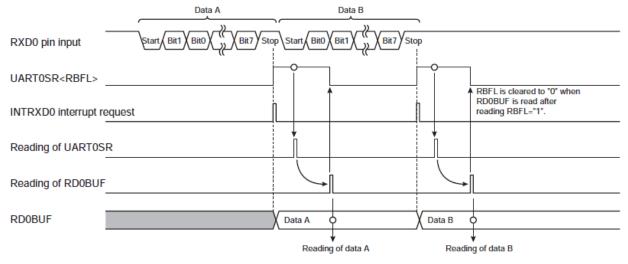

| 13.10.4 接收缓存器已满标帜                      | 270 |

|                                        |     |

Name: SQ7615 中文产品规格书

No.: TDDS01-S7615-CN

### iMQ Technology Inc.

| 13.10.5 发送忙碌标帜                | 270 |

|-------------------------------|-----|

| 13.10.6 发送缓存器已满标帜             | 271 |

| 13.11 接收流程                    | 272 |

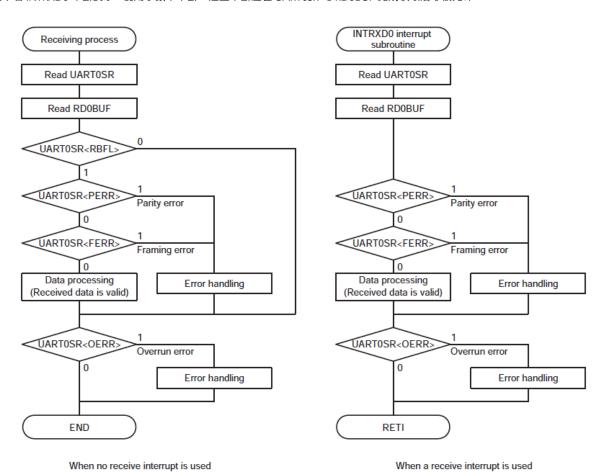

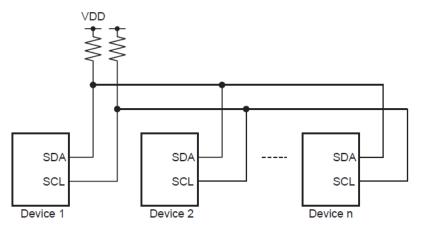

| 14.串行总线接口(SBI)/I2C            | 274 |

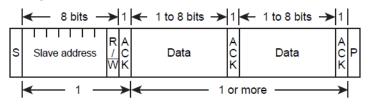

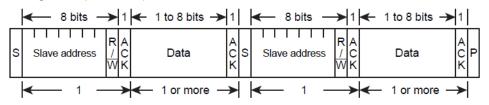

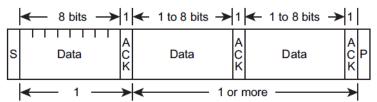

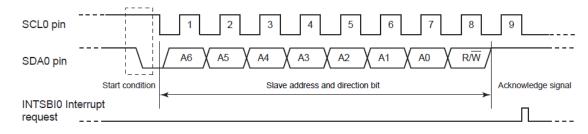

| 14.1 通信格式                     | 274 |

| 14.1.1 I2C 总线                 | 274 |

| 14.1.2 通用数据格式                 | 275 |

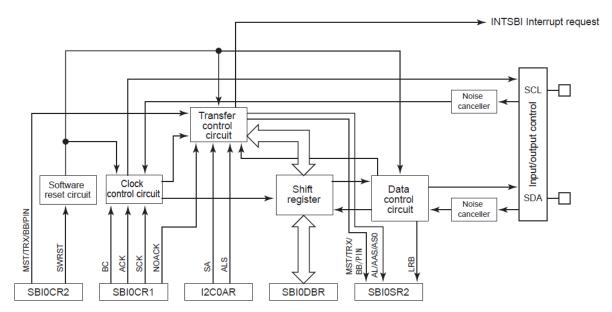

| 14.2 框图                       | 276 |

| 14.3 控制                       | 277 |

| 14.4 功能                       | 283 |

| 14.1.1 低功耗功能                  | 283 |

| 14.1.2 选取从属地址配对检测与广播呼叫检测      | 283 |

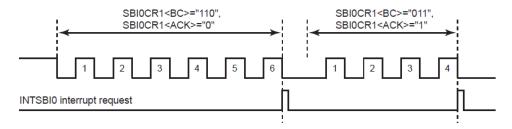

| 14.1.3 选取数据传输的时钟数与选取应答或单一应答模式 | 284 |

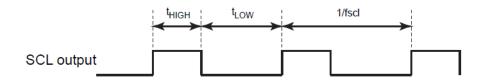

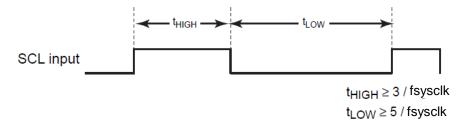

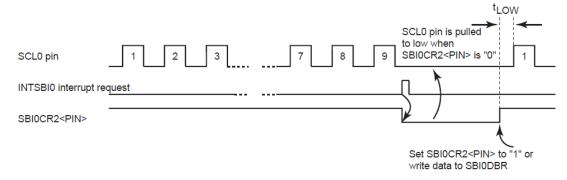

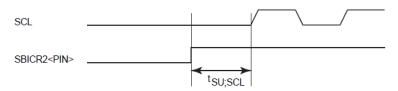

| 144.4 串行时钟                    | 287 |

| 14.4.5 选取主控/从属                | 289 |

| 14.4.6 选取传输/接收                | 289 |

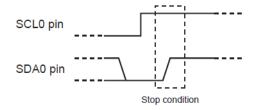

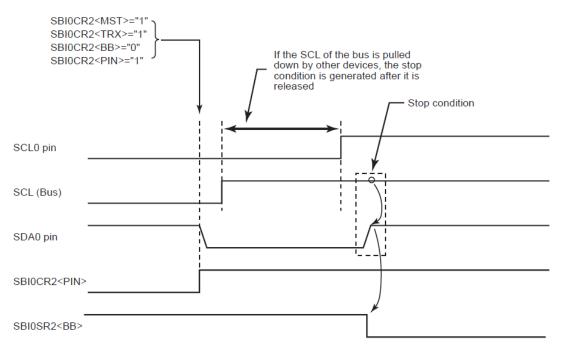

| 14.4.7 生成开始/停止条件              | 290 |

| 14.4.8 中断服务需求发布与释放            | 291 |

| 14.4.9 设定串行总线接口模式             | 291 |

| 14.4.10 软件复位                  | 292 |

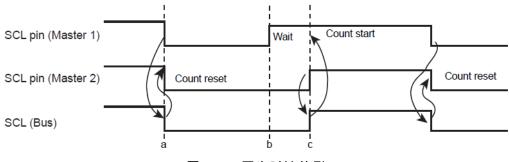

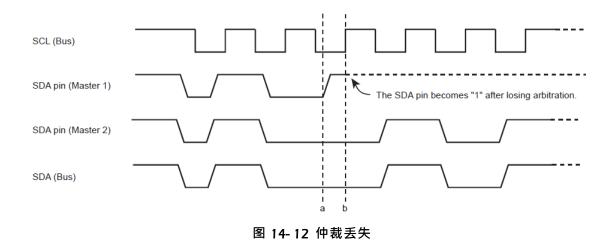

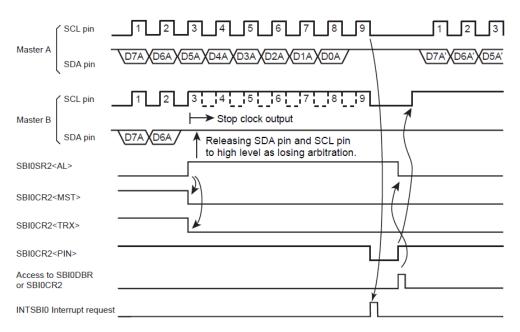

| 14.4.11 仲裁丢失检测功能              | 292 |

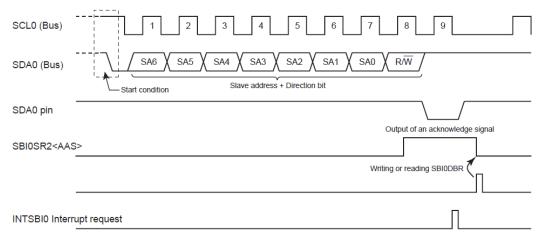

| 14.4.12 从属地址配对检测              | 293 |

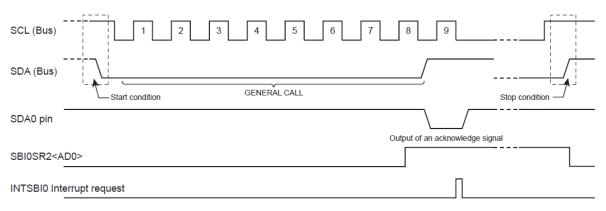

| 14.4.13 广播呼叫检测                | 294 |

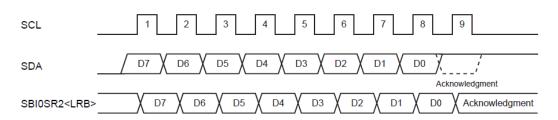

| 14.4.14 最后接收位的监控              | 294 |

| 14.4.15 从属位址与位址辨识模式说明         | 295 |

| 14.5 I2C 总线的数据传输              | 295 |

| 14.5.1 设备初始化                  | 295 |

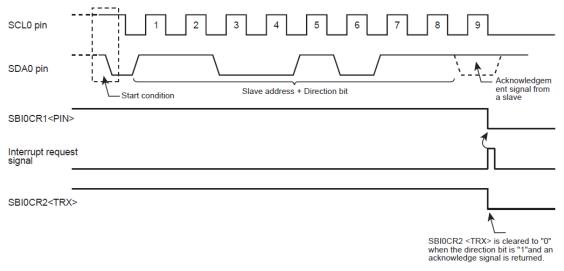

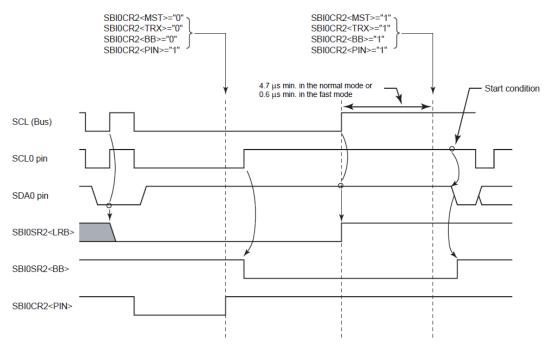

| 14.5.2 开始条件与从属地址产生            | 295 |

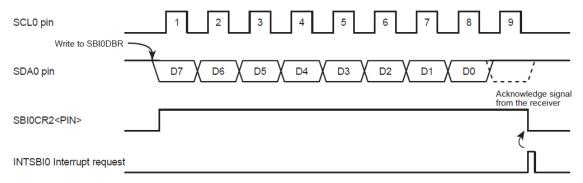

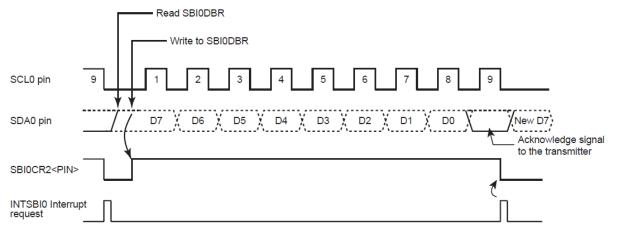

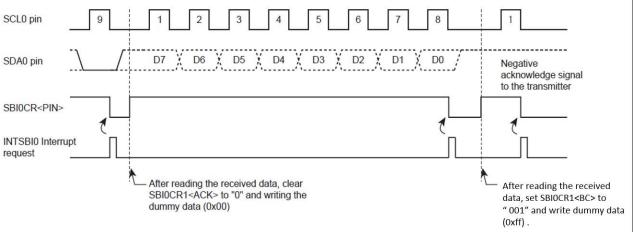

| 14.5.3 字数据传输                  | 296 |

| 14.5.4 停止条件产生                 | 300 |

| 14.5.5 重新启动                   | 301 |

|                               |     |

Name: SQ7615 中文产品规格书

No.: TDDS01-S7615-CN

## iMQ Technology Inc.

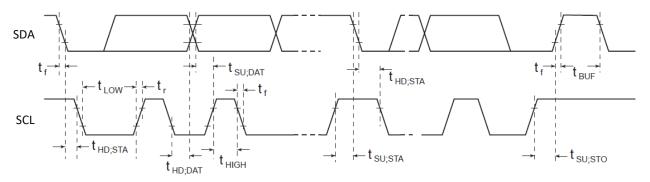

| 14.6 AC 规格                                 | 303 |

|--------------------------------------------|-----|

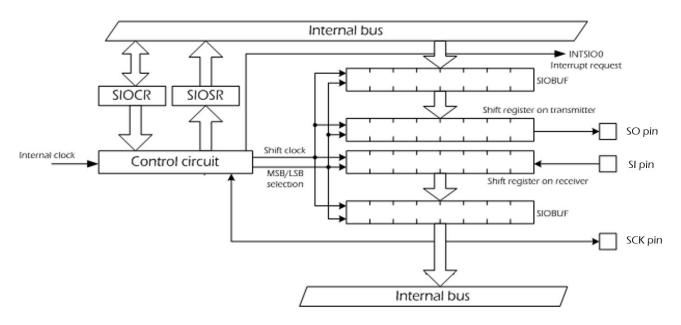

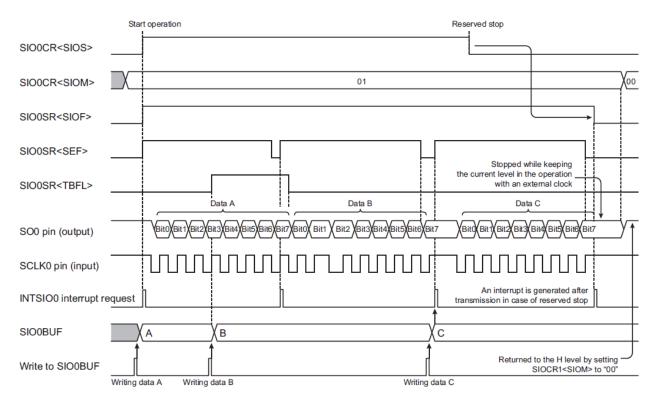

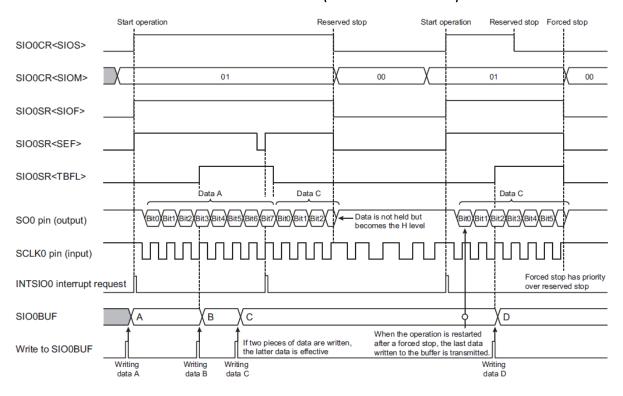

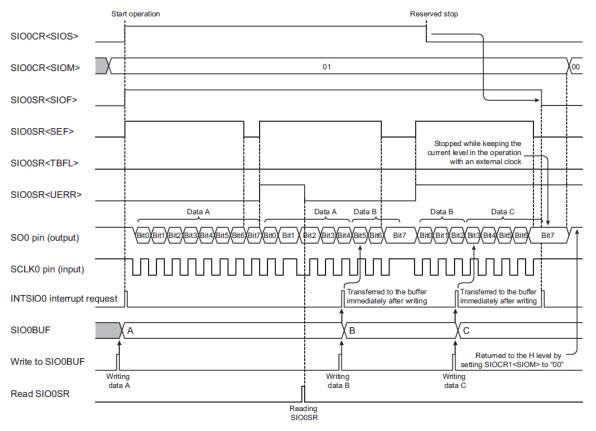

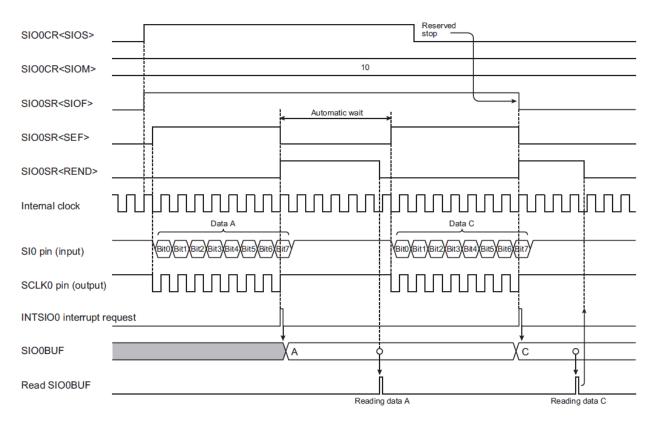

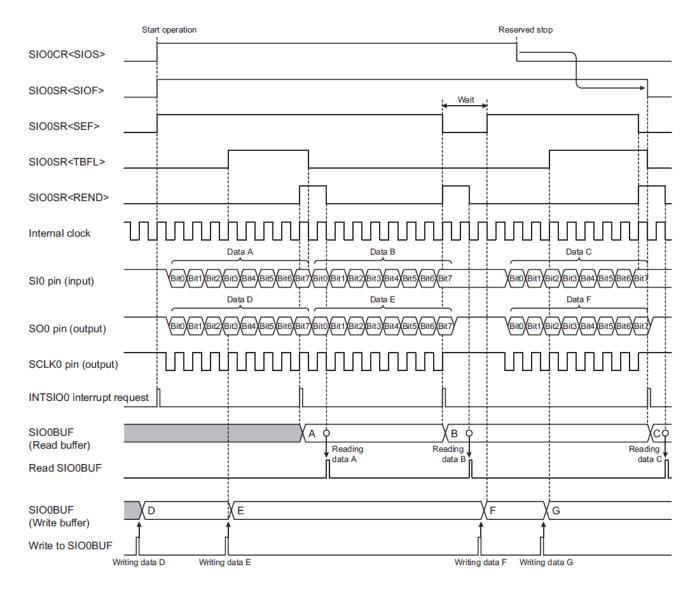

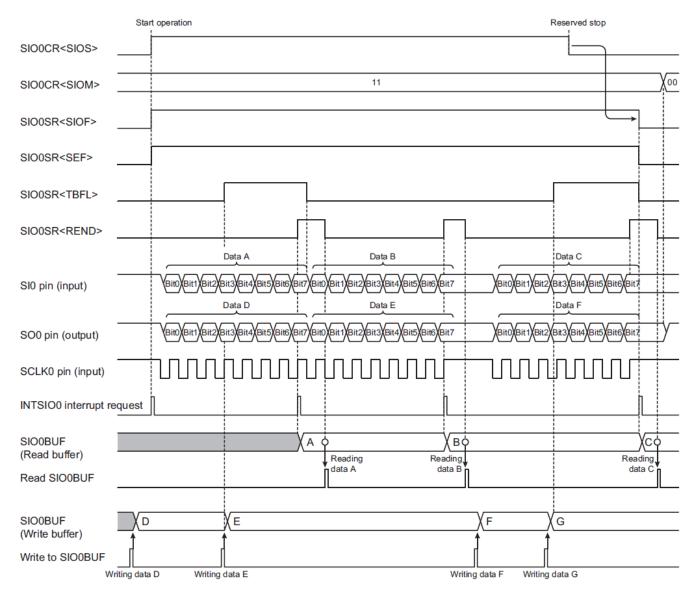

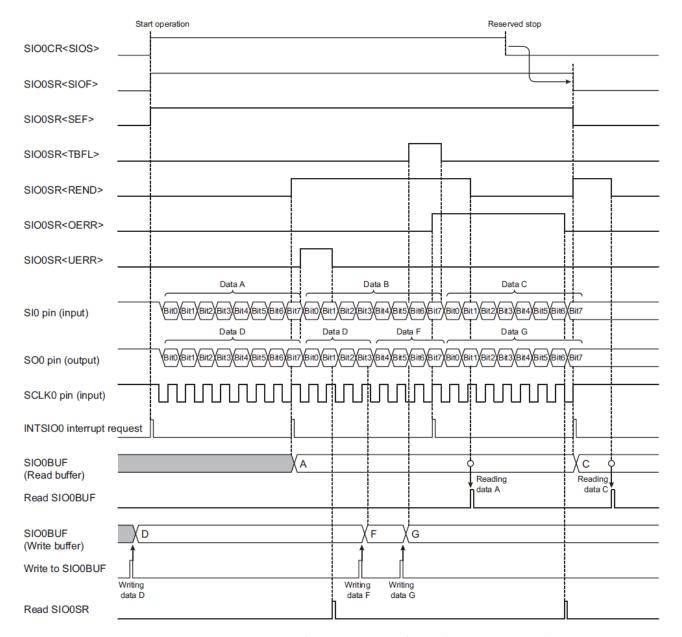

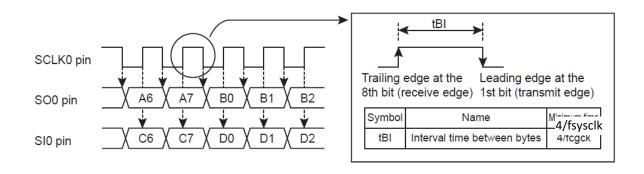

| 15 同步串行收发器(SIO)                            | 305 |

| 15.1 框图                                    | 305 |

| 15.2 控制                                    | 306 |

| 15.3 低耗电功能                                 | 309 |

| 15.4 功能                                    | 310 |

| 15.4.1 传送模式                                | 310 |

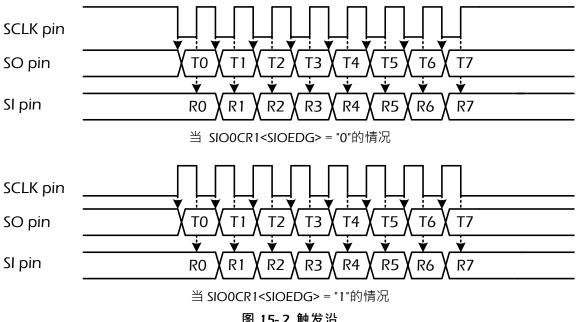

| 15.4.2 串行时钟                                | 310 |

| 15.4.3 触发沿选择                               | 311 |

| 15.5 传送模式                                  | 312 |

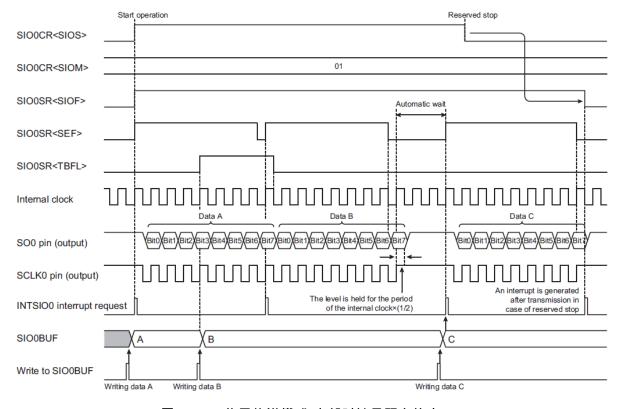

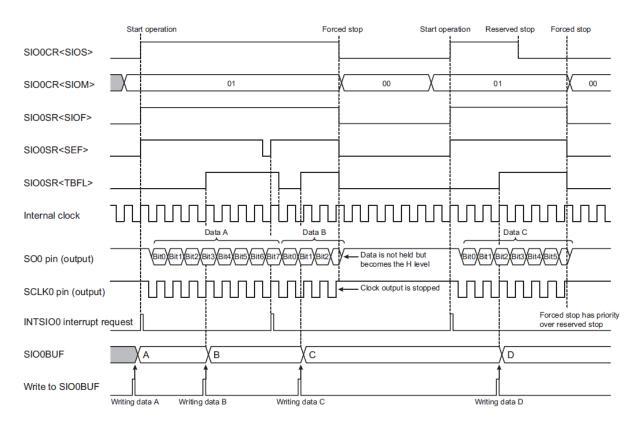

| 15.5.1 8 位传送模式                             | 312 |

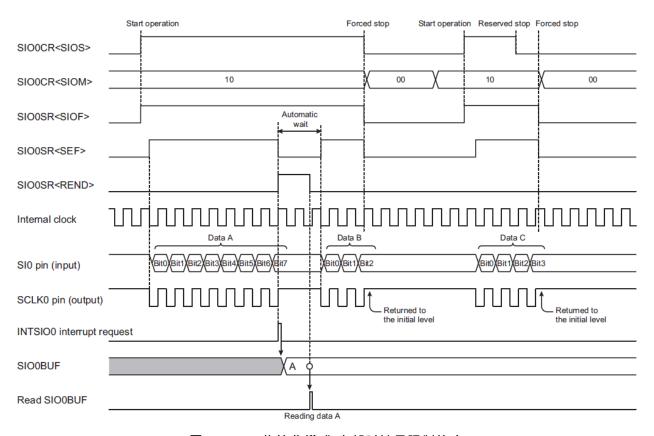

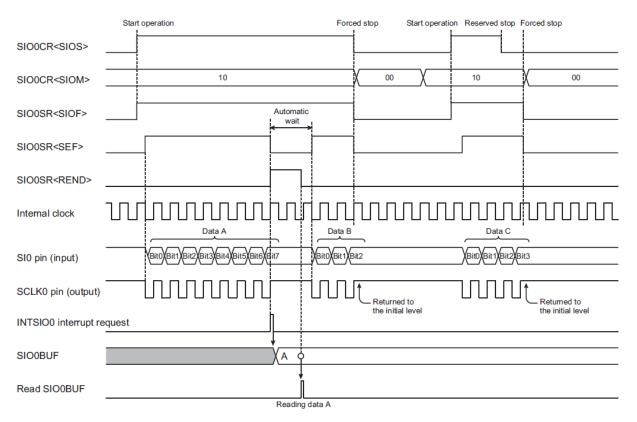

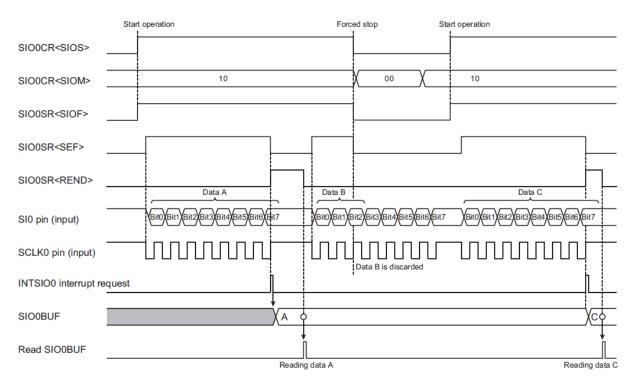

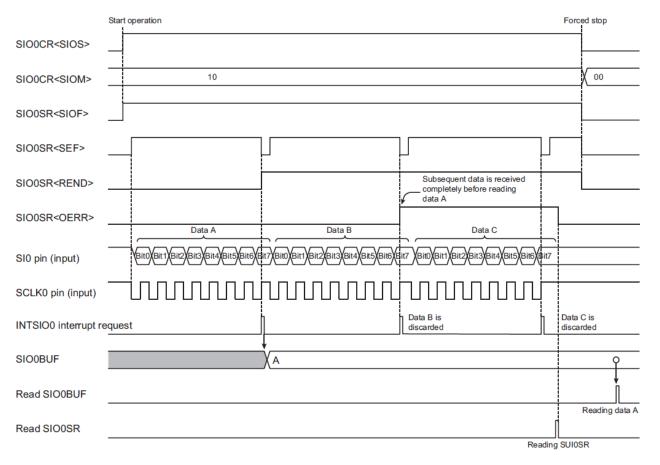

| 15.5.2 8 位接收模式                             | 317 |

| 15.5.3 8 位传送/接收模式                          | 323 |

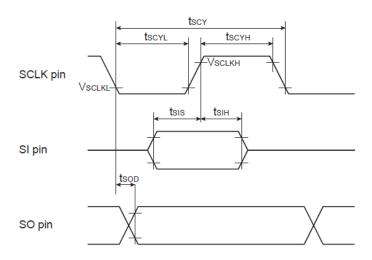

| 15.6 AC 特性                                 | 328 |

| 16 安全功能                                    | 329 |

| 16. 1 循环冗余校验(CYCLIC REDUNDANCY CHECK, CRC) | 329 |

| 16.1.1 CRC 功能概述                            | 329 |

| 16.1.2 CRC 控制寄存器                           | 329 |

| 16. 2 数据正确性确认(Data Integrity Check, DIC)   | 332 |

| 16.2.1 DIC 功能概述                            | 332 |

| 16.2.2 DIC 控制寄存器                           | 334 |

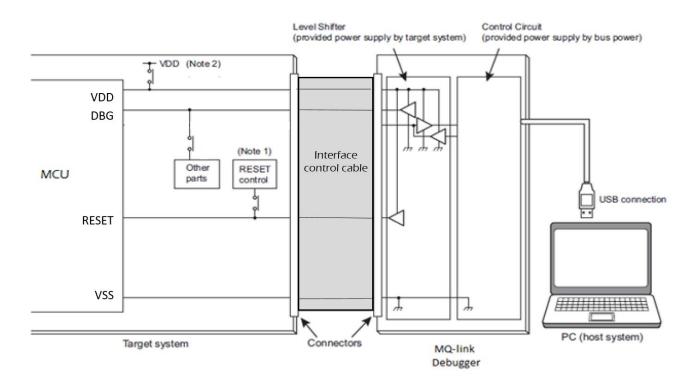

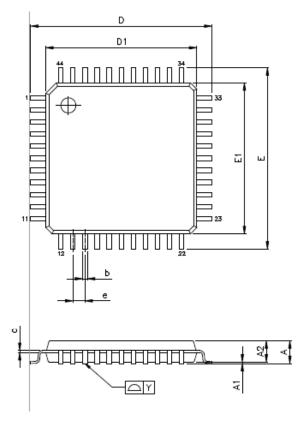

| 附录 A. 仿真调适功能(ON-CHIP DEBUG)                | 337 |

| 附录 B. 产品型号信息                               |     |

| 附录 C. 封装信息                                 | 340 |

| 附录 D. 使用注意事项                               |     |

| 修改记录                                       |     |

|                                            |     |

Name: SQ7615 中文产品规格书

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

## 1.产品简介

## 1.1 功能特性

#### 基本信息

- 工作电压范围: 2.0V ~ 5.5V

- 工作温度范围: -40℃~85℃

- 最高工作频率 24 MHz

- 870E核心完全兼容于Toshiba TLCS-870/C1指令集

#### 存储配置

- 64 KB Flash

- 4 KB RAM

#### 工作功耗

- 普通模式170 uA/MHz@3.3V

- 深眠模式1 uA @ 3.3V, 掉电复位, CPU以 及RAM保持寄存器

- 深眠模式1.6 uA @ 3.3V, RTC启动, LXTAL on, 掉电复位, CPU以及RAM保持 寄存器

#### 多样化系统时钟源

- 16 MHz外部高速时钟

- 32 kHz外部低速时钟

- 锁相环(PLL)

- 多种内部低功耗参考时钟,包含

- 32 kHz

- 16 MHz

#### 1/0

- 最多41个I/O引脚

- 具备3组UART,2组I2C以及2组SIO

#### 内置乘法器与除法器

- 16位乘以16位与32位加法

- 32位除以32位

#### 定时器/计数器

- 8个16位定时器,具计数器,外部触发定时 器,脉宽测量与PPG输出模式

- 具万年历功能之RTC

- 看门狗定时器

#### 中断控制器

8个外部中断输入(EINTO~EINT7)

#### 12位ADC

- 有12个输入埠

- 1个ADC器外部参考电压源选择

### ◆ 低电压检测 (LVD)系统

2.35V/2.65V/2.85V/3.15V/3.98V/4.2V/4.5V

### 掉电复位检测(BROR)系统,共4级

1.9V/2.25V/2.55V/2.75V

#### 安全加密防护功能

- 128-bit UID (Unique ID)

- 程序保护

#### 封装形式

LQFP 10x10 44引脚

#### 应用项目

- 家电应用

- 消费性电子

- 需要保护开发程序之应用

Page: 10/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

No.: TDDS01-S7615-CN Name: SQ7615 中文产品规格书 Version: V1.9

## 1.2 重点说明

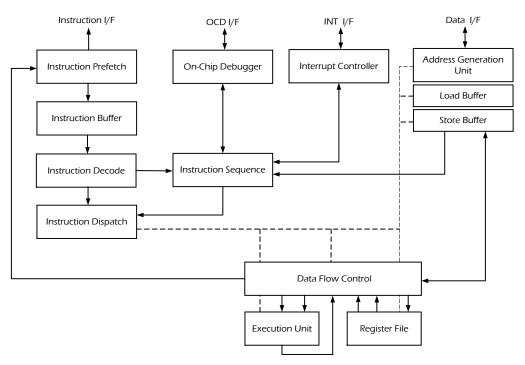

产品使用 SQ8E 自有核心可兼容 TLCS-870/C1 指令集架构,为一高效节能且具低电门数运算核心,其可变长度指令集提供 38 组核心指令,9 种寻址模式以及强大的存储运作,指令操作码长度从 1 位到 5 位,一般指令多为2至4位。

核心为三阶管线设计,指令队列以及核心功能单元可于单周期中频繁执行指令,哈佛结构可使系统同时取出指令以及数据存取,特定硬件专门处理指令与数据对齐,增进工作效能。

内置 64K Flash 存储、4K RAM、多样的 I/O 端口功能、多组定时器与计数器、时钟产生器,以及高精度的 12 位 ADC 器。多种内部与外部时钟源可根据用户所需频率选取,亦可支持数字外设以及精准模拟特性,用户可依性能、耗电等不同需求进行工作模式的优化调整。

图 1-1 核心工作模块图

Page: 11/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

| 产品型号               | SQ7615LA044SETR                                                   |  |  |

|--------------------|-------------------------------------------------------------------|--|--|

| 脚位数                | 44                                                                |  |  |

| (IO 数)             | (41)                                                              |  |  |

| 工作电压               | 2.0~5.5V                                                          |  |  |

| 工作温度               | -40~85C                                                           |  |  |

| 外部唤醒               | 8                                                                 |  |  |

| Flash 容量 /烧写次<br>数 | 64K Bytes/10 万次                                                   |  |  |

| RAM                | 4K Bytes                                                          |  |  |

| ADC                | 12-bit x 12-CH<br>(VDD,外)                                         |  |  |

| 中断                 | 外部: 8<br>内部: <b>29</b>                                            |  |  |

| 内部晶振 / 精准度         | 16MHz<br>+/- 1% @ 0~50C<br>+/- 1.5% @ -20~70C<br>+/- 3% @ -40~85C |  |  |

| 外部晶振               | 1~16MHz 或 32768Hz                                                 |  |  |

| BROR               | 4 级                                                               |  |  |

| 低电压检测              | 8级<br>(+/- 3%)* <sup>2</sup>                                      |  |  |

| 定时器/               | 16bit x 8                                                         |  |  |

| 计数器                | WDT,TBT,RTC                                                       |  |  |

| PWM/PPG            | 16bit x 8                                                         |  |  |

| 传输                 | UART x 3,<br>SIO x 2,<br>I2C x 2                                  |  |  |

| 在线仿真               | 有                                                                 |  |  |

| 烧录                 | OCDE 脚位烧录                                                         |  |  |

| 封装                 | LOFP44                                                            |  |  |

Note 1:「VDD」表示 ADC 使用 VDD 为内部参考电压;「外」表示 ADC 使用外部参考电压。 Note 2: SQ 系列产品具 8 級 LVD·精准度最小可达±3%, 各级的详细规格请参阅产品规格书。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

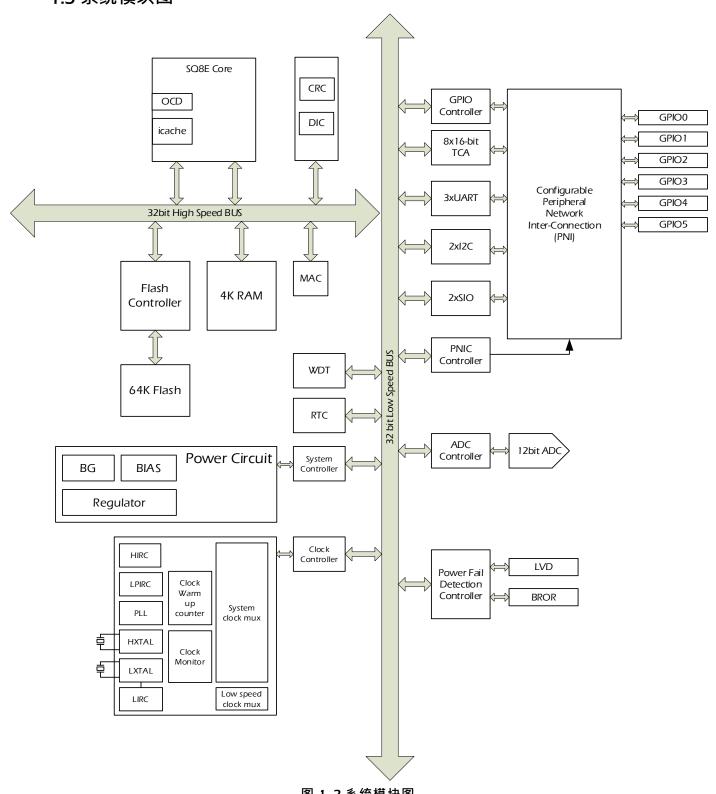

## 1.3 系统模块图

图 1-2 系统模块图

Page: 13/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

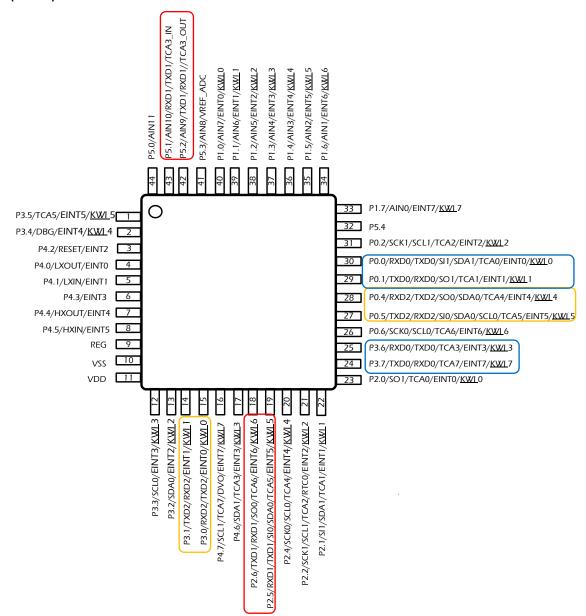

## 1.4 引脚配置/说明

LQFP44 (10x10) - SQ7615LA044SETR

图 1-3 LQFP-44 封装型态引脚配置

注 1:SQ7615 仿真需连接 P3.4/DBG、P4.2/RESET、VDD、GND。客户在系统板上所预留之仿真脚位,请参考外部参考 线路图进行设计,不建议增加其它元器件以免影响仿真特性或功能。

注 2:SQ7615 烧录以 OCDE 脚位脚位进行, 客户在系统板上所预留之烧录脚位, 请参考下图 1-4~ 图 1-7 进行设计, 不建 议增加其它元器件以免影响烧录特性或功能。OCDE 脚位, 相同于仿真脚位(P3.4/DBG、P4.2/RESET、VDD、VSS)。烧录

Page: 14/350 本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

单颗 IC 内的 64KByte 程序空间所需时间约 9 秒。iMO 仿真器(MO-Link)与烧录器(Flash Writer)支持此种烧录模式。(烧录单 颗 IC 时间·为使用 Flash Writer V3.20 测试)。

注 3:TCAx 为 Timer Input/output 功能,但 P5.1/TCA3\_IN 为 Timer Input 功能,P5.2/TCA3\_OUT 为 Timer output 功 能。

注 4: UART 脚位需依以下配對使用,若选择 P0.0 为 RXD0,则需使用 P0.1 为 TXD0。:

| UART0 | TXD0/RXD0 | P0.0/RXD0/TXD0<br>P0.1/TXD0/RXD0 | P3.6/RXD0/TXD0<br>P3.7/TXD0/RXD0 |

|-------|-----------|----------------------------------|----------------------------------|

| UART1 | TXD1/RXD1 | P2.5/RXD1/TXD1<br>P2.6/TXD1/RXD1 | P5.1/RXD1/TXD1<br>P5.2/TXD1/RXD1 |

| UART2 | TXD2/RXD2 | P0.4/RXD2/TXD2<br>P0.5/TXD2/RXD2 | P3.0/RXD2/TXD2<br>P3.1/TXD2/RXD2 |

| I2C0 | SCL0/SDA0 | P0.6/SCL0<br>P0.5/SDA0 | P0.5/SCL0<br>P0.4/SDA0 | P2.4/SCL0<br>P2.5/SDA0 | P3.3/SCL0<br>P3.2/SDA0 |

|------|-----------|------------------------|------------------------|------------------------|------------------------|

| I2C1 | SCL1/SDA1 | P0.2/SCL1<br>P0.0/SDA1 | P2.2/SCL1<br>P2.1/SDA1 | P4.7/SCL1<br>P4.6/SDA1 |                        |

| SIO0 | SCK0/ SI0/ SO0 | P0.6/SCK0<br>P0.5/SI0<br>P0.4/SO0  | P2.4/SCLK0<br>P2.5/SI0<br>P2.6/ SO0   |

|------|----------------|------------------------------------|---------------------------------------|

| SIO1 | SCK1/SI1 / SO1 | P0.2/SCLK1<br>P0.0/SI1<br>P0.1/SO1 | P2.2/ SCLK1<br>P2.1/ SI1<br>P2.0/ SO1 |

注 5: I/O 与唤醒、外部中断对照表如下:

|        |      | 引脚名称 |              |      | 引脚/端口功能                          |       |  |

|--------|------|------|--------------|------|----------------------------------|-------|--|

| コロル中有が |      |      |              |      | Key-on Wakeup External Interrupt |       |  |

| P0.0   | P1.0 | P2.0 | P3.0         |      | <u>KWI</u> 0                     | EINT0 |  |

| P0.1   | P1.1 | P2.1 | P3.1         |      | <u>KWI</u> 1                     | EINT1 |  |

| P0.2   | P1.2 | P2.2 | P3.2         |      | <u>KWI</u> 2                     | EINT2 |  |

| -      | P1.3 | -    | P3.3<br>P3.6 | P4.6 | <u>KWI</u> 3                     | EINT3 |  |

| P0.4   | P1.4 | P2.4 | P3.4         |      | <u>KWI</u> 4                     | EINT4 |  |

| P0.5   | P1.5 | P2.5 | P3.5         |      | <u>KWI</u> 5                     | EINT5 |  |

| P0.6   | P1.6 | P2.6 | -            | -    | <u>KWI</u> 6                     | EINT6 |  |

| -      | P1.7 | -    | P3.7         | P4.7 | <u>KWI</u> 7                     | EINT7 |  |

|        |      |      |              | P4.0 |                                  | EINT0 |  |

|        |      |      |              | P4.1 |                                  | EINT1 |  |

|        |      |      |              | P4.2 |                                  | EINT2 |  |

|        |      |      |              | P4.3 |                                  | EINT3 |  |

|        |      |      |              | P4.4 |                                  | EINT4 |  |

|        |      |      |              | P4.5 |                                  | EINT5 |  |

#### iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

| 44引脚<br>编号 | 引脚名称与端口/选择功能          | I/O类型           | 功能叙述                                                                                                      |

|------------|-----------------------|-----------------|-----------------------------------------------------------------------------------------------------------|

| 1          | P3.5/ TCA5/EINT5/KWI5 | I/O<br>(Type A) | P3.5为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>外部中断EINT5、唤醒输入引脚KWI5、16位定时器/计数器引脚TCA5与P3.5共享引脚。               |

| 2          | P3.4/ DBG/EINT4/KWI4  | I/O<br>(Type A) | P3.4为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>外部中断EINT4、唤醒输入引脚KWI4、在线烧录DBG引脚与P3.4共享引脚。                      |

| 3          | P4.2/RESET/EINT2      | I/O<br>(Type A) | P4.2为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下<br>拉电阻。<br>外部中断EINT2与P4.2共享引脚。<br>RESET与P4.2共享引脚·为低电平有效(low-active)。 |

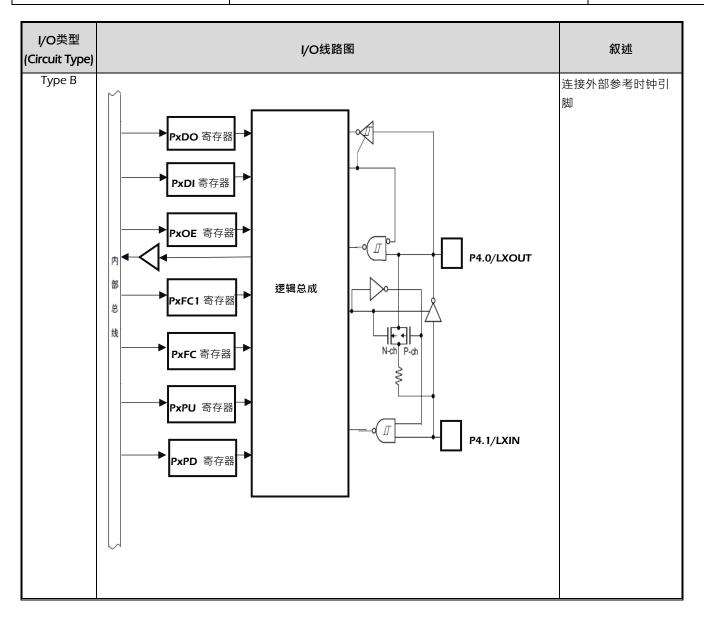

| 4          | P4.0/LXOUT/EINT0      | I/O<br>(Type B) | P4.0为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下<br>拉电阻。<br>低速外部参考时钟连接LXOUT、外部中断EINT0与P4.0共享引脚。                       |

| 5          | P4.1/LXIN/EINT1       | I/O<br>(Type B) | P4.1为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下<br>拉电阻。<br>低速外部参考时钟连接 LXIN、外部中断EINT1与P4.1共享引脚。                       |

| 6          | P4.3/EINT3            | I/O<br>(Type A) | P4.3为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>外部中断EINT3与P4.3共享引脚。                                           |

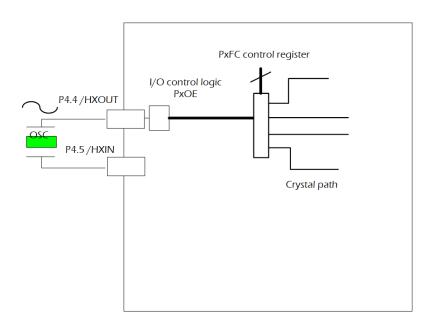

| 7          | P4.4/HXOUT/EINT4      | I/O<br>(Type B) | P4.4为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下<br>拉电阻。<br>高速外部参考时钟连接 HXOUT、外部中断EINT4与P4.4共享引脚。                      |

| 8          | P4.5/HXIN/EINT5       | I/O<br>(Type B) | P4.5为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下<br>拉电阻。<br>高速外部参考时钟连接 HXIN、外部中断EINT5与P4.5共享引脚。                       |

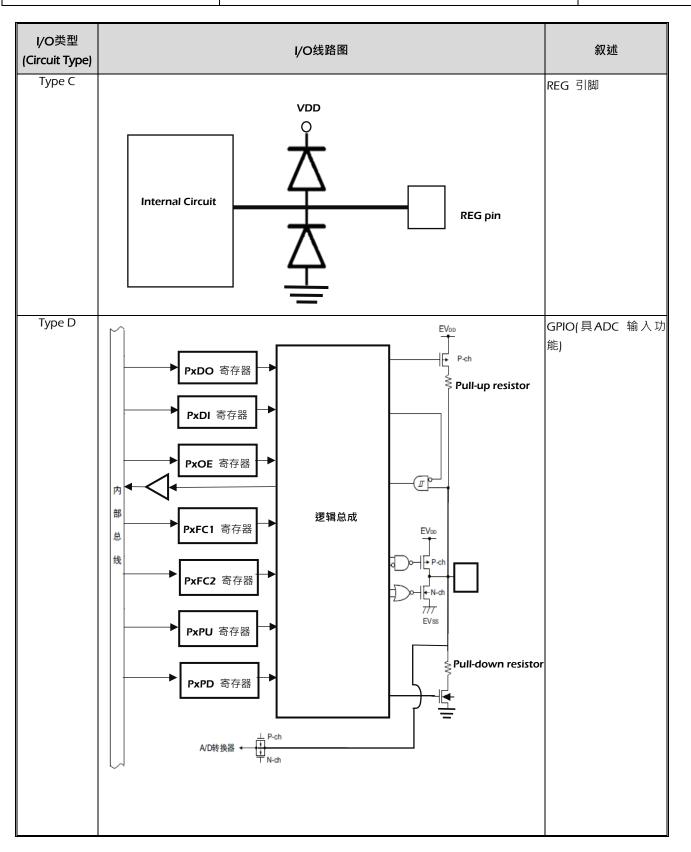

| 9          | REG                   | -<br>(Type C)   | 注:REG pin无法供电给外部线路使用                                                                                      |

| 10         | VSS                   | 电源              | 接地电源输入                                                                                                    |

| 11         | VDD                   | 电源              | VDD电源输入                                                                                                   |

| 12         | P3.3/SCL0/EINT3/KWI3  | I/O<br>(TypeA)  | P3.3为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>I2C引脚SCLO、外部中断EINT3、唤醒输入引脚KWI 3与P3.3共享引脚。                     |

| 13         | P3.2/SDA0/EINT2/KWI2  | I/O<br>(Type A) | P3.2为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>I2C引脚SDA0、外部中断EINT2、唤醒输入引脚KWI 2与P3.2共享引脚。                     |

Page: 16/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

## iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

| 44引脚<br>编号 | 引脚名称与<br>端口/选择功能                              | I/O类型           | 功能叙述                                                                                                                 |

|------------|-----------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------|

| 14         | P3.1/TXD2/RXD2/ EINT1/KWI1                    | I/O<br>(Type A) | P3.1为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>UART引脚TXD2/RXD2、外部中断EINT1、唤醒输入引脚KWI 1与P3.1共享引脚。                          |

| 15         | P3.0/RXD2/TXD2/ EINT0/KWI0                    | I/O<br>(Type A) | P3.0为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 UART引脚RXD2/TXD2、外部中断EINTO、唤醒输入引脚KWI 0与P3.0共享引脚。                             |

| 16         | P4.7/SCL1/TCA7 /DVO/ EINT7<br>/KWI7           | I/O<br>(Type A) | P4.7为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 I2C引脚SCL1、16位定时器TCA7、分频器输出DVO引脚DVO、外部中断EINT7、唤醒输入引脚KWI7与P4.7共享引脚。           |

| 17         | P4.6/SDA1/TCA3/ EINT3 /KWI3                   | I/O<br>(Type A) | P4.6为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 I2C引脚SDA1、16位定时器TCA3、外部中断EINT3、唤醒输入引脚KWI 3与P4.6共享引脚。                        |

| 18         | P2.6/TXD1/RXD1/SO0/TCA6/<br>EINT6 /KWI6       | I/O<br>(Type A) | P2.6为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 UART引脚TXD1/RXD1、SIO引脚SOO、16位定时器TCA6、外部中断EINT6、唤醒输入引脚KWI6与P2.6共享引脚。          |

|            | P2.5/RXD1/TXD1/SI0/SDA0/TC<br>A5/ EINT5 /KWI5 | I/O<br>(Type A) | P2.5为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 UART引脚RXD1/TXD1、SIO引脚SIO、I2C引腳SDA、16位定时器TCA5、外部中断EINT5、唤醒输入引脚KWI5与P2.5共享引脚。 |

| 20         | P2.4/SCK0/SCL0/TCA4 / EINT4<br>/KWI4          | I/O<br>(Type A) | P2.4为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 SIO引脚SCKO、I2C引腳SCLO、16位定时器TCA4、外部中断EINT4、唤醒输入引脚KWI4与P2.4共享引脚。               |

| 21         | P2.2/SCK1/SCL1/TCA2/ EINT2<br>/KWI2/RTC0      | I/O<br>(Type A) | P2.2为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 SIO引脚SCK1、I2C引腳SCL1、16位定时器TCA2、外部中断EINT2、唤醒输入引脚KWI2、RTC0与P2.2共享引脚。          |

| 22         | P2.1/SI1/SDA1/TCA1/ EINT1<br>/KWI1            | I/O<br>(Type A) | P2.1为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 SIO引脚SI1、I2C引腳SDA1、16位定时器TCA1、外部中断EINT1、唤醒输入引脚KWI1与P2.1共享引脚。                |

| 23         | P2.0/SO1/TCA0/ EINT0 /KWI0                    | I/O<br>(Type A) | P2.0为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 SIO引脚SO1、16位定时器TCA0、外部中断EINTO、唤醒输入引脚KWIO与P2.0共享引脚。                          |

Page: 17/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

## iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

| 44引脚<br>编号 | 引脚名称与端口/选择功能                                       | I/O类型           | 功能叙述                                                                                                                   |

|------------|----------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------|

| 24         | P3.7/TXD0/RXD0/TCA7/ EINT7<br>/KWI7                | I/O<br>(Type A) | P3.7为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 UART引脚TXD0/RXD0、16位定时器TCA7、外部中断EINT7、唤醒输入引脚KWI7与P3.7共享引脚。                     |

| 25         | P3.6/RXD0/TXD0/TCA3/ EINT3<br>/KWI3                | I/O<br>(Type A) | P3.6为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 UART引脚RXD0/TXD0、16位定时器TCA3、外部中断EINT3、唤醒输入引脚KWI3与P3.6共享引脚。                     |

| 26         | P0.6/SCK0/SCL0/TCA6/ EINT6<br>/KWI6                | I/O<br>(Type A) | P0.6为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 SIO引脚SCKO、I2C引脚SCLO、16位定时器TCA6、外部中断EINT6、唤醒输入引脚KWI6与0.6共享引脚。                  |

| 27         | P0.5/TXD2/RXD2/SI0/SDA0/SC<br>L0/TCA5/ EINT5 /KWI5 | I/O<br>(Type A) | P0.5为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 UART引脚TXD2/RXD2、SIO引脚SIO、I2C引脚SDAO、16位定时器TCA5、外部中断EINT5、唤醒输入引脚KWI5与P0.5共享引脚。  |

| 28         | P0.4/RXD2/TXD2/SO0/SDA0/T<br>CA4/ EINT4 /KWI4      | I/O<br>(Type A) | P0.4为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 UART引脚RXD2/TXD2、SIO引脚SO0、I2C引脚SDA0、16位定时器TCA4、外部中断EINT4、唤醒输入引脚KWI4与P0.4共享引脚。  |

| 29         | P0.1/TXD0/RXD0/SO1/TCA1 /<br>EINT1 /KWI1           | I/O<br>(Type A) | P0.1为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 UART引脚TXD0/RXD0、SIO引脚SO1、16位定时器TCA1、外部中断 EINT1、唤醒输入引脚KWI1与P0.1共享引脚。           |

| 30         | P0.0/RXD0/TXD0/SI1/SDA1/TC<br>A0/EINT0 /KWI0       | I/O<br>(Type A) | P0.0为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 UART引脚RXD0/TXD0、SIO引脚SI1、I2C引脚SDA1、16位定时器 TCA0、外部中断EINTO、唤醒输入引脚KWI0与P0.0共享引脚。 |

| 31         | P0.2/ SCLK1/SCL1/TCA2/EINT2<br>/KWI2               | I/O<br>(Type A) | P0.2为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 SIO引脚SCLK1、I2C引脚SCL1、16位定时器TCA2、外部中断EINT2、唤醒输入引脚KWI2与P0.2共享引脚。                |

| 32         | P5.4                                               | I/O<br>(Type A) | P5.4为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。                                                                               |

| 33         | P1.7/AIN0/EINT7 /KWI7                              | I/O<br>(Type D) | P1.7为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>ADC输入AINO、外部中断EINT7、唤醒输入引脚KWI7与P1.7共享引脚。                                   |

Page: 18/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

No.: TDDS01-S7615-CN Name: SQ7615 中文产品规格书 Version: V1.9

| 44引脚<br>编号 | 引脚名称与端口/选择功能                     | I/O类型           | 功能叙述                                                                                            |

|------------|----------------------------------|-----------------|-------------------------------------------------------------------------------------------------|

| 34         | P1.6/AIN1/EINT6 /KWI6            | I/O<br>(Type D) | P1.6为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>ADC 输入 AIN1、外部中断 EINT6、唤醒输入引脚 KWI6 与 P1.6 共享引脚。     |

| 35         | P1.5/AIN2/EINT5 /KWI5            | I/O<br>(Type D) | P1.5为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>ADC 输入 AIN2、外部中断 EINT5、唤醒输入引脚 KWI5 与 P1.5 共享引脚。     |

| 36         | P1.4/AIN3/EINT4 /KWI4            | I/O<br>(Type D) | P1.4为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下<br>拉电阻。<br>ADC 输入 AIN3、外部中断 EINT4、唤醒输入引脚 KWI4 与 P1.4 共享引脚。 |

| 37         | P1.3/AIN4/EINT3 /KWI3            | I/O<br>(Type D) | P1.3为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下<br>拉电阻。<br>ADC输入AIN4、外部中断EINT3、唤醒输入引脚KWI3与P1.3共享引脚。        |

| 38         | P1.2/AIN5/EINT2 /KWI2            | I/O<br>(Type D) | P1.2为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>ADC输入AIN5、外部中断EINT2、唤醒输入引脚KWI2与P1.2共享引脚。            |

| 39         | P1.1/AIN6/EINT1 /KWI1            | I/O<br>(Type D) | P1.1为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>ADC输入AIN6、外部中断EINT1、唤醒输入引脚KWI1与P1.1共享引脚。            |

| 40         | P1.0/AIN7/EINT0 /KWI0            | I/O<br>(Type D) | P1.0为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>ADC输入AIN7、外部中断EINTO、唤醒输入引脚KWIO与P1.0共享引脚。            |

| 41         | P5.3/AIN8/VREF_ ADC              | I/O<br>(Type D) | P5.3为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>ADC输入AIN8、ADC参考电压输入 VREF_ADC与 P5.3共享引脚。             |

| 42         | P5.2/AIN9/TXD1/RXD1/TCA3_<br>OUT | I/O<br>(Type D) | P5.2为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。 ADC输入AIN9、UART脚TXD1/RXD1、16位定时器TCA3_OUT与P5.2共享引脚。      |

| 43         | P5.1/AIN10/RXD1/TXD1/TCA3<br>_IN | I/O<br>(Type D) | P5.1为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>ADC输入AIN10、UART脚RXD1/TXD1、16位定时器TCA3_IN与P5.1共享引脚。   |

| 44         | P5.0/AIN11                       | I/O<br>(Type D) | P5.0为双向可编程I/O端口·可以软件编程设定连接引脚内置上拉电阻或下拉电阻。<br>ADC输入AIN11与P5.0共享引脚。                                |

注 1:4 线仿真需连接 P3.4/DBG、P4.2/RESET、VDD、GND。

Page: 19/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

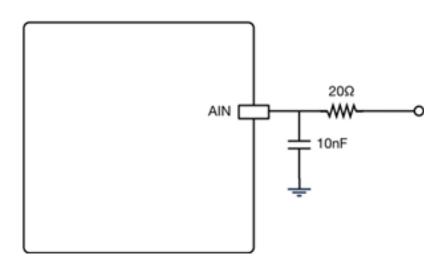

以下为在使用 SQ7615 产品时建议的外部参考线路,若使用到相关引脚功能时,请参考所对应的接线建议:

#### 1. 进行 ADC 输入滤波:

## **ADC Input Filter**

图 1-4 建议外部参考线路(进行 ADC 输入滤波)

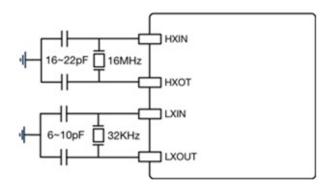

#### 2. 使用外部参考时钟引脚:

#### External Crystal

图 1-5 建议外部参考线路(使用外部参考时钟引脚)

Page: 20/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

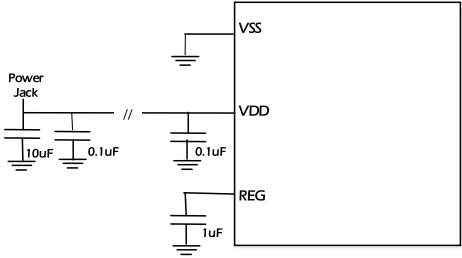

#### 3. 电源去耦(power decoupling):

## Power Decoupling Cap

图 1-6 建议外部参考线路(电源去耦-POWER DECOUPLING)

注:上图近 IC 端(VDD)的 0.1uF,应该尽可能靠近 IC

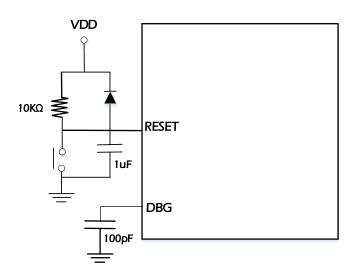

#### 4. 复位引脚与仿真引脚:

图 1-7 建议外部参考线路(复位引脚与仿真引脚)

Page: 21/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

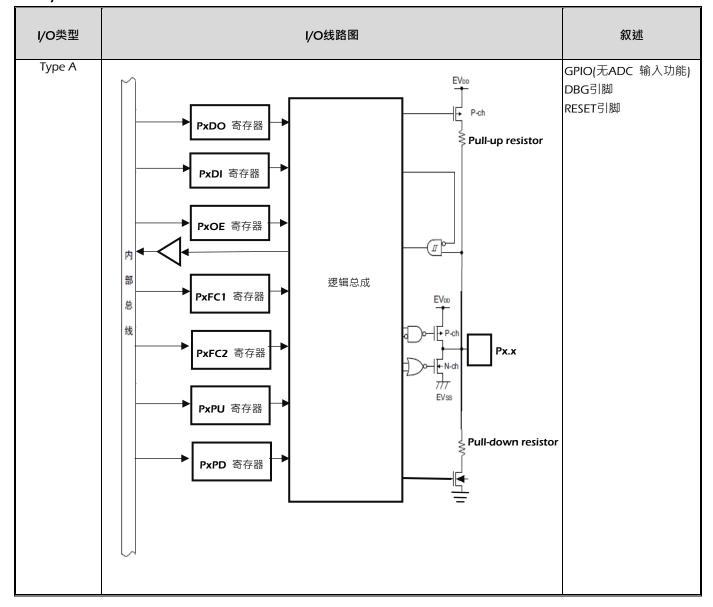

## 1.5 I/O 线路图

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

Page: 23/350 本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

Page: 24/350 本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

## 2.电气特性

## 2.1 极限参数

单片机操作时切勿超过以下任一项极限参数值。即使仅是极短时间,也可能造成单片机损坏或性能衰退, 严重者可能导致起火或爆炸、造成伤害。因此,请确保采用本单片机设计开发之产品 或系统不超过以下极 限参数值。

$(V_{SS} = 0V)$

| 参数     | 符号               | 引脚        | 极限参数            | 单位 |

|--------|------------------|-----------|-----------------|----|

| 工作电压范围 | $V_{DD}$         |           | -0.3 to 6.0     | V  |

| 输入电压范围 | V <sub>IN</sub>  | 全部数位元引脚   | -0.3 to VDD+0.3 | V  |

| 最大输出电流 |                  | 全部 I/O 引脚 | 100             | mA |

| 储存温度范围 | T <sub>STG</sub> |           | -50 to 125      | °C |

iMQ Technology Inc.

No.: TDDS01-S7615-CN Name: SQ7615 中文产品规格书 Version: V1.9

## 2.2 工作条件

以下定义出当装置于电压及温度最大/最小值运行时其电气特性。除非另有说明,否则标准条件是在「室温 25℃及标准工作电压 V<sub>DD</sub>=3.3V」下测定而得。

#### 2.2.1 工作条件

| 参数      | 符号        | 测试条件 | 最小   | 标准   | 最大   | 单位 |

|---------|-----------|------|------|------|------|----|

| 工作电压    | $V_{DD}$  |      | 2.0  | 3.3  | 5.5  | V  |

| 模拟工作电压  | $V_{DDA}$ |      | 2.0  | 3.3  | 5.5  | V  |

| 复位电压(注) | $V_{RST}$ |      | 1.89 | 1.95 | 2.01 | V  |

| 工作温度    | Ta        |      | -40  | 25   | 85   | °C |

注:复位电压使用 BROR 第一阶

#### 2.2.2 时钟源

| 参数          | 符号                 | 测试条件                             | 最小     | 标准    | 最大     | 单位     |

|-------------|--------------------|----------------------------------|--------|-------|--------|--------|

| 外部时钟源       |                    |                                  |        |       |        |        |

| 外部低速时钟(注 1) | f <sub>LXIN</sub>  |                                  |        | 32768 |        | Hz     |

| 外部高速时钟(注 1) | f <sub>XIN</sub>   |                                  | 1      |       | 16     | MHz    |

| 内部时钟源       | 1                  |                                  | 1      | •     | 1      |        |

| 内部低速时钟      | $f_{LIRC}$         | T <sub>A</sub> = 25°C            | -25%   | 32    | + 25%  | kHz    |

|             |                    | T <sub>A</sub> = 25°C            | - 1%   | 1     | + 1%   | MHz    |

|             | ٤                  | T <sub>A</sub> = 0~ 50°C (注 2)   | - 1%   | 1     | + 1%   |        |

| 低功耗内部时钟     | f <sub>LPIRC</sub> | T <sub>A</sub> = -20~ 70°C (注 2) | - 1.5% | 1     | + 1.5% |        |

|             |                    | T <sub>A</sub> = -40~ 85°C       | - 3%   | 1     | + 3%   |        |

|             |                    | T <sub>A</sub> = 25°C            | - 1%   | 16    | + 1%   |        |

| 中如京油叶林      | £                  | T <sub>A</sub> = 0~ 50°C (注 2)   | - 1%   | 16    | + 1%   | NAL 1- |

| 内部高速时钟      | f <sub>HIRC</sub>  | T <sub>A</sub> = -20~ 70°C (注 2) | - 1.5% | 16    | + 1.5% | MHz    |

|             |                    | T <sub>A</sub> = -40~ 85°C       | - 3%   | 16    | + 3%   |        |

| 锁相环         | f <sub>PLL</sub>   | T <sub>A</sub> = 25°C            | (注 3)  | 24    | (注 3)  | MHz    |

注 1:外部高速时钟在启动后到完全起振約 2.5ms(16MHz, 25℃); 外部低速时钟在启动后到完全起振約 1.2 sec(32KHz,

25°C) ∘

注 2: 此规格为 VDD= 5V ±10%(即 4.5~5.5V)条件下。

注 3:锁相环( $f_{PLL}$ ) 精准度同 PLL 时钟源(16MHz 外部高速时钟  $f_{XIN}$  与低功耗内部时钟  $f_{LPIRC}$ ),为+/- 1%。

Page: 26/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

## 2.2.3 I/O 特性

|            | VDD=3.3V ,Ta=-40~85°C |            |          |     |          |    |  |  |

|------------|-----------------------|------------|----------|-----|----------|----|--|--|

| 参数         | 符号                    | 测试条件       | 最小       | 标准  | 最大       | 单位 |  |  |

| 低电压输入      | V <sub>IL</sub>       |            | 0        |     | 0.25 VDD | V  |  |  |

| 高电压输入      | VIH                   |            | 0.75 VDD |     | VDD      | V  |  |  |

| 端口引脚之低电压输出 | V <sub>OL_050</sub>   | IOL=5 mA   |          |     | 0.4      | V  |  |  |

| 端口引脚之高电压输出 | V <sub>OH_015</sub>   | IOH=1.5 mA | VDD-0.4  |     |          | V  |  |  |

| 低电平输出电流    |                       | 0.1xVDD    | 2.5      | 6.7 |          | mA |  |  |

| 1500年刊山电流  | l <sub>OL</sub>       | 0.3xVDD    | 7        | 15  |          | mA |  |  |

| 京中亚岭山中沟    |                       | 0.9xVDD    | 1        | 2.4 | -        | mA |  |  |

| 高电平输出电流    | I <sub>OH</sub>       | 0.7xVDD    | 3        | 5.8 |          | mA |  |  |

| 上拉电阻       | R <sub>PULLUP</sub>   |            | 10       | 20  | 40       | kΩ |  |  |

| 下拉电阻       | R <sub>PULLDN</sub>   |            | 10       | 20  | 40       | kΩ |  |  |

| VDD=5V ,Ta=-40~85 |                     |             |          |      |          |    |

|-------------------|---------------------|-------------|----------|------|----------|----|

| 参数                | 符号                  | 测试条件        | 最小       | 标准   | 最大       | 单位 |

| 低电压输入             | V <sub>IL</sub>     |             | 0        |      | 0.25 VDD | V  |

| 高电压输入             | V <sub>IH</sub>     |             | 0.75 VDD |      | VDD      | V  |

| 端口引脚之低电压输出        | V <sub>OL_100</sub> | IOL=10 mA   |          |      | 0.6      | V  |

| 端口引脚之高电压输出        | V <sub>OH_035</sub> | IOH= 3.5 mA | VDD-0.6  |      |          | V  |

| 低电平输出电流           |                     | 0.1xVDD     | 6        | 13.5 |          | mA |

| 15.6一种山电流         | l <sub>OL</sub>     | 0.3xVDD     | 15       | 31   |          | mA |

| 高电平输出电流           |                     | 0.9xVDD     | 2.5      | 4.8  | -        | mA |

| 同电十期山电 <u>派</u>   | Іон                 | 0.7xVDD     | 6.5      | 12   |          | mA |

| 上拉电阻              | R <sub>PULLUP</sub> |             | 10       | 20   | 40       | kΩ |

| 下拉电阻              | R <sub>PULLDN</sub> |             | 10       | 20   | 40       | kΩ |

Page: 27/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

## 2.3 直流(DC)特性

|                                  |                     |                                                                                     | Ор | erating @ 3 | .3V, Ta=-40 | )~85°C |

|----------------------------------|---------------------|-------------------------------------------------------------------------------------|----|-------------|-------------|--------|

| 参数                               | 符号                  | 测试条件                                                                                | 最小 | 标准          | 最大          | 单位     |

|                                  | I <sub>DD_N0</sub>  | LPIRC 为 PLL 时钟源,<br>系统时钟为 24MHz,<br>f <sub>LPIRC</sub> =1MHz,fsysclk=24MHz<br>(PLL) | -  | 5.5         | 8.5         | mA     |

| 普通模式                             | I <sub>DD_N1</sub>  | 内部高速时钟(HIRC)为系统时钟 ,<br>f <sub>HXIN</sub> =0MHz,fsysclk=16 MHz<br>(HIRC)             | -  | 2.7         | 4.2         | mA     |

| 自避侯八<br>(LIRC 启动・由 Flash 执行)     | I <sub>DD_N2</sub>  | LIRC 为系统时钟<br>所有时钟都关闭,仅 LIRC 启动,<br>fsysclk=32KHz                                   | -  | 0.7         | 1.1         | mA     |

|                                  | I <sub>DD_N3</sub>  | 外部高速时钟(HXTAL)为系统时钟<br>fsysclk=16MHz<br>(HXTAL)                                      | -  | 3.8         | 5.7         | mA     |

|                                  | I <sub>DD_N4</sub>  | 外部低速时钟(LXTAL)为系统时钟<br>fsysclk=32768Hz<br>(LXTAL)                                    | -  | 0.7         | 1.1         | mA     |

|                                  | I <sub>DD_SL0</sub> | LPIRC 为 PLL 时钟源,<br>系统时钟为 24MHz,<br>f <sub>LPIRC</sub> =1MHz,fsysclk=24MHz<br>(PLL) | -  | 2.7         | 4.1         | mA     |

| 睡眠模式                             | I <sub>DD_SL1</sub> | 内部高速时钟(HIRC)为系统时钟 ,<br>f <sub>HXIN</sub> =0MHz,HIRC 16 MHz<br>(HIRC)                | -  | 1.3         | 2.1         | mA     |

| (LIRC 启动·CPU 时钟停止运               | I <sub>DD_SL2</sub> | LIRC 为系统时钟<br>fsysclk=32KHz                                                         | -  | 0.7         | 1.1         | mA     |

| 行)                               | I <sub>DD_SL3</sub> | 外部高速时钟(HXTAL)为系统时钟<br>fsysclk=16MHz<br>(HXTAL)                                      | -  | 2.0         | 3.1         | mA     |

|                                  | I <sub>DD_SL4</sub> | 外部低速时钟(LXTAL)为系统时钟<br>fsysclk=32768Hz<br>(LXTAL)                                    | -  | 0.7         | 1.1         | mA     |

| 深眠模式                             | I <sub>DD_DS0</sub> | RTC 不启动                                                                             |    | 1.0         | -           | uA     |

| (LIRC 启动·CPU 以及 RAM<br>为保持寄存器模式) | I <sub>DD_DS1</sub> | RTC 启动, LXTAL on                                                                    |    | 1.6         | -           | uA     |

| Operating @ 3.3V, Ta=25                  |                     |                  |     |     |    |    |  |  |

|------------------------------------------|---------------------|------------------|-----|-----|----|----|--|--|

| 参数                                       | 符号                  | 测试条件             | 最小  | 标准  | 最大 | 单位 |  |  |

| 深眠模式<br>(LIRC 启动·CPU 以及 RAM<br>为保持寄存器模式) | I <sub>DD_DS0</sub> | RTC 不启动          | 0.8 | 1.0 | -  | uA |  |  |

|                                          | I <sub>DD_DS1</sub> | RTC 启动, LXTAL on | 1.4 | 1.6 | -  | uA |  |  |

Page: 28/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

|                                  | Operating @ 5V,Ta=-40~85°0       |                                                                                     |    |     |     | 0~85°C |

|----------------------------------|----------------------------------|-------------------------------------------------------------------------------------|----|-----|-----|--------|

| 参数                               | 符号                               | 测试条件                                                                                | 最小 | 标准  | 最大  | 单位     |

|                                  | I <sub>DD_N0</sub>               | LPIRC 为 PLL 时钟源,<br>系统时钟为 24MHz,<br>f <sub>LPIRC</sub> =1MHz,fsysclk=24MHz<br>(PLL) | -  | 5.5 | 8.5 | mA     |

| 普通模式                             | I <sub>DD_N1</sub>               | 内部高速时钟(HIRC)为系统时钟,<br>f <sub>HXIN</sub> =0MHz,fsysclk=16 MHz<br>(HIRC)              | -  | 2.7 | 4.2 | mA     |

| ョ 世代式<br>(LIRC 启动・由 Flash 执行)    | I <sub>DD_N2</sub>               | LIRC 为系统时钟<br>所有时钟都关闭,仅 LIRC 启动,<br>fsysclk=32KHz                                   | -  | 0.8 | 1.2 | mA     |

|                                  | I <sub>DD_N3</sub>               | 外部高速时钟(HXTAL)为系统时钟<br>fsysclk=16MHz<br>(HXTAL)                                      | -  | 3.8 | 5.7 | mA     |

|                                  | $I_{\mathrm{DD}_{-}\mathrm{N4}}$ | 外部低速时钟(LXTAL)为系统时钟<br>fsysclk=32768Hz<br>(LXTAL)                                    | -  | 0.8 | 1.2 | mA     |

|                                  | I <sub>DD_SL0</sub>              | LPIRC 为 PLL 时钟源,<br>系统时钟为 24MHz,<br>f <sub>LPIRC</sub> =1MHz,fsysclk=24MHz<br>(PLL) | -  | 2.7 | 4.1 | mA     |

| 睡眠模式                             | I <sub>DD_SL1</sub>              | 内部高速时钟(HIRC)为系统时钟 ,<br>f <sub>HXIN</sub> =0MHz,HIRC 16 MHz<br>(HIRC)                | -  | 1.3 | 2.1 | mA     |

| (LIRC 启动·CPU 时钟停止运               | I <sub>DD_SL2</sub>              | LIRC 为系统时钟<br>fsysclk=32KHz                                                         | -  | 0.8 | 1.2 | mA     |

| 行)                               | I <sub>DD_SL3</sub>              | 外部高速时钟(HXTAL)为系统时钟<br>fsysclk=16MHz<br>(HXTAL)                                      | -  | 2.0 | 3.1 | mA     |

|                                  | I <sub>DD_SL4</sub>              | 外部低速时钟(LXTAL)为系统时钟<br>fsysclk=32768Hz<br>(LXTAL)                                    | -  | 0.8 | 1.2 | mA     |

| 深眠模式                             | I <sub>DD_DS0</sub>              | RTC 不启动                                                                             | -  | 1.1 | -   | uA     |

| (LIRC 启动·CPU 以及 RAM<br>为保持寄存器模式) | I <sub>DD_DS1</sub>              | RTC 启动, LXTAL on                                                                    | -  | 1.8 | -   | uA     |

| Operating @ 5V,Ta=25°C           |                     |                  |     |     |    |    |  |

|----------------------------------|---------------------|------------------|-----|-----|----|----|--|

| 参数                               | 符号                  | 测试条件             | 最小  | 标准  | 最大 | 单位 |  |

| 深眠模式                             | I <sub>DD_DS0</sub> | RTC 不启动          | 0.9 | 1.1 | -  | uA |  |

| (LIRC 启动·CPU 以及 RAM<br>为保持寄存器模式) | I <sub>DD_DS1</sub> | RTC 启动, LXTAL on | 1.5 | 1.8 | -  | uA |  |

Page: 29/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

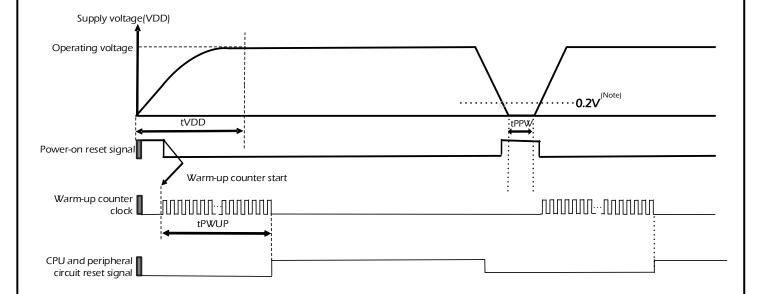

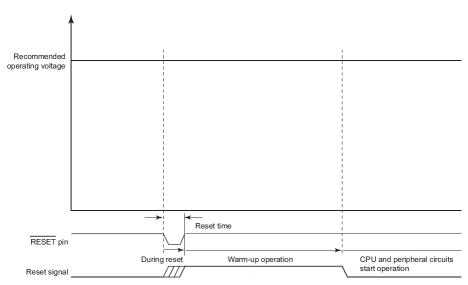

## 2.4 上电复位电气特性

|       |                                                                                |     |    | Ta= | -40~85°C |

|-------|--------------------------------------------------------------------------------|-----|----|-----|----------|

| 符号    | 叙述                                                                             | 最小  | 标准 | 最大  | 单位       |

| tPPW  | 上电复位最小脉宽<br>Power-on reset minimum pulse width                                 | 1   | -  | -   | ms       |

| tPWUP | 上电复位后到 CPU ready 时间(注)<br>Warming-up time after a reset is clear and CPU ready | 1   | 4  | -   | ms       |

| tVDD  | 上电时间<br>Power supply rise time                                                 | 0.5 | -  | 5   | ms       |

注: 此 tPWUP 不包含 BOOTROM code 执行时间; BOOTROM code 执行时间约需 50ms。

图 2-1 上电复位时序图

Note: 当系统下电时, 电压需低于 0.2V 再重新上电, 才能确保重新上电后的 IC 动作正常。

Page: 30/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

No.: TDDS01-S7615-CN Name: SQ7615 中文产品规格书 Version: V1.9

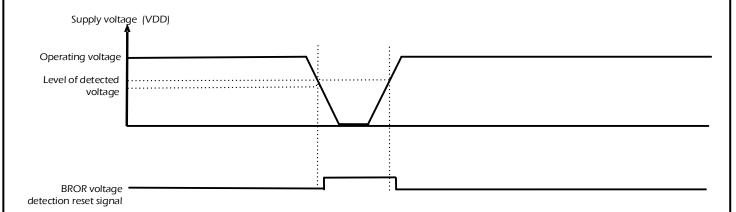

## 2.5 BROR 电气特性

|               |           |                |      |      | Ta=-4 | 0~85°C |

|---------------|-----------|----------------|------|------|-------|--------|

| 参数            | 符号        | 测试条件           | 最小   | 标准   | 最大    | 单位     |

|               | VBRORON1  | 第一阶,BRORCFG=00 | 1.84 | 1.90 | 1.96  | V      |

|               | VBROROFF1 | 第一例,BKOKCFG=00 | 1.89 | 1.95 | 2.01  | V      |

|               | VBRORON2  | 第二阶,BRORCFG=01 | 2.18 | 2.25 | 2.32  | V      |

| BROR detected | VBROROFF2 |                | 2.23 | 2.30 | 2.37  | V      |

| voltage       | VBRORON3  | 第三阶,BRORCFG=10 | 2.47 | 2.55 | 2.63  | V      |

|               | VBROROFF3 |                | 2.52 | 2.60 | 2.68  | V      |

|               | VBRORON4  |                | 2.67 | 2.75 | 2.83  | V      |

|               | VBROROFF4 | 第四阶,BRORCFG=11 | 2.72 | 2.80 | 2.88  | V      |

图 2-2 BROR 复位

Note: 当发生 BROR 时,请勿再执行任何动作。

Page: 31/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

No.: TDDS01-S7615-CN Name: SQ7615 中文产品规格书 Version: V1.9

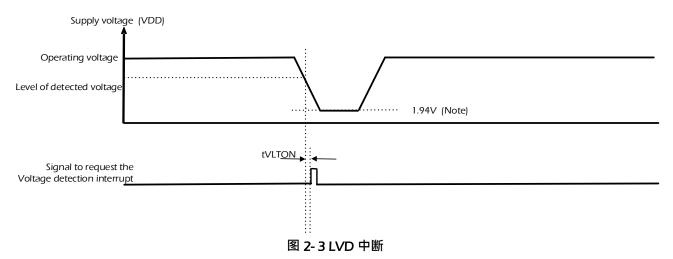

## 2.6 LVD 电气特性

|          |       |                                     |      |      | Ta=-4 | 0~85°C |

|----------|-------|-------------------------------------|------|------|-------|--------|

| 参数       | 符号    | 测试条件                                | 最小   | 标准   | 最大    | 单位     |

|          | VLVD1 | Falling Mode,第一阶, LVDCFG=000 (Note) | 1.94 | 2.00 | 2.06  | V      |

|          | VLVD2 | Falling Mode,第二阶, LVDCFG=001        | 2.28 | 2.35 | 2.42  | V      |

|          | VLVD3 | Falling Mode,第三阶, LVDCFG=010        | 2.57 | 2.65 | 2.73  | V      |

| LVD 检测电压 | VLVD4 | Falling Mode,第四阶, LVDCFG=011        | 2.76 | 2.85 | 2.94  | V      |

| LVU 位则电压 | VLVD5 | Falling Mode,第五阶, LVDCFG=100        | 3.06 | 3.15 | 3.24  | V      |

|          | VLVD6 | Falling Mode,第六阶, LVDCFG=101        | 3.86 | 3.98 | 4.1   | V      |

|          | VLVD7 | Falling Mode,第七阶, LVDCFG=110        | 4.07 | 4.20 | 4.33  | V      |

|          | VLVD8 | Falling Mode,第八阶, LVDCFG=111        | 4.37 | 4.50 | 4.64  | V      |

| ぞ   | 符号   | 叙述                                        | 最小 | 标准 | 最大 | 单位 |

|-----|------|-------------------------------------------|----|----|----|----|

| tVL | LTON | Voltage detecting detection response time | -  | 1  | 10 | us |

Note:可能会触发 BROR

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

## 2.7 ADC 电气特性

VREF\_ADC=VDD 45\/ < \/DD < 55\/ T<sub>4</sub>= -45~85°C

|              |                      | 4.   | $5V \ge VL$ | $JU \ge 5.5$     | $V, I_A = -4$ | 15~85 C |

|--------------|----------------------|------|-------------|------------------|---------------|---------|

| 参数           | 符号                   | 测试条件 | 最小          | 标准               | 最大            | 单位      |

| 分辨率          | RES <sub>ADC</sub>   |      |             | 12               |               | bits    |

| 最大转换速率       | f <sub>ADC</sub>     |      |             |                  | 470           | KSPS    |

| 微分非线性误差(DNL) | DNL <sub>ADC</sub>   |      |             |                  | ±2.5          | LSB     |

| 积分非线性误差(INL) | INL <sub>ADC</sub>   |      |             |                  | ±3.5          | LSB     |

| 绝对增益精度       | E <sub>GAIN</sub>    |      |             |                  | ±5            | LSB     |

| 偏移误差         | E <sub>OFFSET</sub>  |      |             |                  | ±4.5          | LSB     |

| 输入电压范围       | $V_{ADC\_RNG}$       |      |             |                  | VDD           | V       |

| VREF_ADC电压范围 | V <sub>REF_ADC</sub> |      |             | VDD <sup>注</sup> |               | V       |

|              |                      | ·    |             |                  |               |         |

注:VREF\_ADC=VDD,电压范围 2~5.5V

VREF\_ADC=VDD

$2V \le VDD \le 5.5V T_A = -45 \sim 85^{\circ}C$

|              |                      |      | $ZV \geq VL$ | $D \geq 0.5$     | 0V, IA4 | 5~65 C |

|--------------|----------------------|------|--------------|------------------|---------|--------|

| 参数           | 符号                   | 测试条件 | 最小           | 标准               | 最大      | 单位     |

| 分辨率          | RES <sub>ADC</sub>   |      |              | 12               |         | bits   |

| 最大转换速率       | f <sub>ADC</sub>     |      |              |                  | 470     | KSPS   |

| 微分非线性误差(DNL) | DNL <sub>ADC</sub>   |      |              |                  | ±4      | LSB    |

| 积分非线性误差(INL) | INL <sub>ADC</sub>   |      |              |                  | ±5      | LSB    |

| 绝对增益精度       | E <sub>GAIN</sub>    |      |              |                  | ±6      | LSB    |

| 偏移误差         | E <sub>OFFSET</sub>  |      |              |                  | ±6      | LSB    |

| 输入电压范围       | $V_{ADC\_RNG}$       |      |              |                  | VDD     | V      |

| VREF_ADC电压范围 | V <sub>REF_ADC</sub> |      |              | VDD <sup>注</sup> |         | V      |

注:VREF\_ADC=VDD,电压范围 2~5.5V

$注: ADC sample rate= \frac{1}{22} \times \frac{fsysclk}{ADCCKDIV}$

当系统主频为 24MHz, ADCCKDIV 设为 0x02 · ADC Sample rate :  $\frac{1}{22}x\frac{24MHz}{2^2} = 272.727ksps$

Page: 33/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

No.: TDDS01-S7615-CN Name: SQ7615 中文产品规格书 Version: V1.9

## 2.8 Flash 电气特性

$(V_{SS} = 0V, 2.0V \le V_{DD} \le 5.5V, T_{OPR} = -40 \text{ to } 85^{\circ}C)$

| 参数              | 测试条件              | 最小 | 标准 | 最大      | 单位 |

|-----------------|-------------------|----|----|---------|----|

| Flash 存储器保证烧写次数 |                   | _  | _  | 100,000 | 次  |

| Flash 存储器烧写时间   | 烧写时间(per byte)    | _  | _  | 7.5     | μs |

|                 | 整颗擦除 chip erase   | _  | _  | 40      |    |

| Flash 存储器擦除时间   | 区块擦除 sector erase |    |    | F       | ms |

|                 | (1 区块 = 512 字节)   | _  |    | 5       |    |

Page: 34/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

## 3. 中央处理器(CPU)

产品架构为 870E 核心

- 丰富指令集可支持 C 语言编码更精简

- 9种寻址模式

- 乘法与除法器指令

- 位操作指令

- 16 位算数逻辑单元(ALU)及下载/储存指令

- 跳转与呼叫指令

- 寄存器文件支持快速上下文切换

- 2个8位以及16位通用寄存器(GPRs)

- 2组8个8位GPRs

- 2组8个16位GPRs

- 16 位程序计数器(PC)

- 16 位堆栈指针(SP)

- 7 位程序状态字 (PSW)

- 存储空间

- 64 KB Flash

- 4KB RAM

Page: 35/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

## 3.1 符号对照

| 符号    | 描述                           | 符号                | 描述                                    |

|-------|------------------------------|-------------------|---------------------------------------|

| А     | A register                   | r,g               | 8-bit register                        |

| W     | W register                   | rr, gg            | 16-bit register                       |

| В     | B register                   | n                 | 4-bit or 8-bit immediate data         |

| С     | C register                   | mn                | 16-bit immediate data                 |

| D     | D register                   | d                 | Signed 5-bit or 8-bit displacement    |

| Е     | E register                   | х,у               | 8-bit direct address                  |

| Н     | H register                   | vw, uz            | 16-bit direct address                 |

|       | Logistor                     | (VV)              | Memory contents at the address        |

| L     | L register                   | (XX)              | specified by XX                       |

| WA    | W/A register                 | /vv±1 VV)         | Two consecutive bytes from the memory |

| WA    | WA register                  | (xx+1, XX)        | location specified by XX              |

| ВС    | BC register                  | b                 | Bit number (0 to 7)                   |

| DE    | DE register                  | .b                | Content of bit specified by b         |

| HL    | HL register                  | $\leftrightarrow$ | Exchange                              |

| IX    | IX register                  | +                 | Add                                   |

| IY    | IY register                  | -                 | Subtract                              |

| PC    | Program Counter              | х                 | Multiply                              |

| SP    | Stack Pointer                | ÷                 | Division                              |

| PSW   | Program Status Word          | &                 | Bitwise AND                           |

| JF    | Jump Status flag             | 1                 | Bitwise OR                            |

| CF    | Carry flag                   | ۸                 | Bitwise exclusive OR                  |

| HF    | Half carry flag              | null              | No operation                          |

| SF    | Cian floa                    | ė                 | Start address of instruction being    |

| 21    | Sign flag                    | \$                | executed                              |

| VF    | Overflow flag                | (src)             | Source memory                         |

| /CF   | Inverse of carry flag        | (dst)             | Destination memory                    |

| IMF   | Interrupt Master Enable flag | (srcdst)          | Source and destination memory         |

| NxtOp | Address of next operation    | RBS               | Register Bank Selector                |

表 3-1 文件内所使用符号

# iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

| 助记符   | 描述                                  | 助记符   | 描述                                     |

|-------|-------------------------------------|-------|----------------------------------------|

| ADD   | Add                                 | OR    | Logical OR                             |

| ADDC  | Add with carry                      | POP   | Pop up                                 |

| AND   | Logical AND                         | PUSH  | Push down                              |

| CALL  | Call                                | RET   | Return from subroutine                 |

| CALLV | Vector call                         | RETI  | Return from maskable interrupt service |

|       |                                     |       | routine                                |

| CLR   | Clear bit/byte                      | RETN  | Return from non-maskable interrupt     |

|       |                                     |       | service routine                        |

| CMP   | Compare                             | ROLC  | Rotate left through carry              |

| DAA   | Decimal adjust for 8-bit addition   | ROLD  | Rotate left digit                      |

| DAS   | Decimal adjust of 8-bit subtraction | RORC  | Rotate right through carry             |

| DEC   | Decrement byte/word (Register)      | RORD  | Rotate right digit                     |

| DI*   | Disable maskable interrupt          | SET   | Bit test and set                       |

| DIV   | Divide byte quotient                | SHLC  | Logical shift left                     |

| EI*   | Enable interrupt                    | SHLCA | Arithmetic shift left                  |

| INC   | Increment byte/word (Register)      | SHRC  | Logical shift right                    |

| J*    | Optimized jump                      | SHRCA | Arithmetic shift right                 |

| JP    | Absolute jump                       | SUB   | Subtract                               |

| JR    | Relative jump                       | SUBB  | Subtract with borrow                   |

| JRS   | Short relative jump                 | SWAP  | swap nibble                            |

| LD    | Load bit/byte/word                  | SWI   | Software interrupt                     |

|       | (Register)/effective address        |       |                                        |

| LDW   | Load word (Memory)                  | TEST* | Bit test                               |

| MUL   | Multiply                            | XCH   | Exchange                               |

| NEG   | Negate                              | XOR   | Logical exclusive OR                   |

| NOP   | No operation                        | OR    | Logical OR                             |

表 3-2 指令助记符

注: 上方标注星号(\*)之指令助记符为扩充汇编机器指令

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

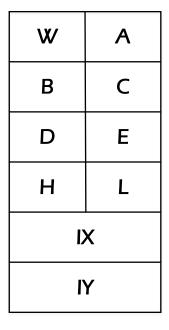

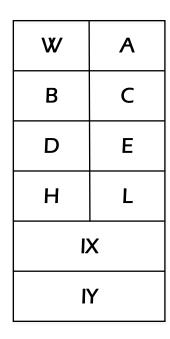

# 3.2 核心寄存器

寄存器组及核心寄存器如下图

Bank0

Bank1

图 3-1 核心寄存器

#### 3.2.1 8 位通用寄存器

产品拥有2组相同的寄存器组、每组皆由8个8位寄存器所组成、这些通用寄存器是W、A、B、C、D、E、H 及 L。这些寄存器也可相互配对成 16 位寄存器对 WA、BC、DE 以及 HL。当系统复位时,这些寄存器亦会复位 为 0。

下列各章节将分别描述寄存器的特殊用途。

### A 寄存器

利用 A 寄存器,位操作指令可指定一寄存器中的某个位,测试其数值或令其改变数值。A 寄存器也可支持 PC 相 对寄存器间接寻址。

范例如下:

SET (0x56).A ; A 寄存器指定存储器 0x0056 位置并设置为 1 LD A(PC+A) ;加载存储器 PC+A 位置之内容至 A 寄存器

Page: 38/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

#### iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

#### C寄存器

于除法指令中·C寄存器作为除数寄存器·亦可于寄存器索引寻址时作为补偿值之寄存器。

范例如下:

DIV WA, C ; C 为除数

LD A,(HL+C) ; C 为偏移量补偿寄存器

#### DE 寄存器

于寄存器间接寻址时,此 16 位 DE 寄存器保存操作数所在的存储器地址。

范例如下:

LD A, (DE) ; DE 为保存存储器地址之寄存器

#### HL 寄存器

寄存器间接寻址时,此 16 位 HL 寄存器保存操作数所在的存储器地址。索引寻址时,HL 寄存器当作索引寄存器 使用。

#### 范例如下:

LD A, (HL) ; HL 为保存存储器地址之寄存器

LD A, (HL+0x52) ; HL 为索引寄存器

LD A,(HL+C) ; HL 为索引寄存器

#### 3.2.2 16 位通用寄存器

产品有 2 个 16 位通用寄存器 IX 和 IY。寄存器间接寻址时,IX 和 IY 寄存器保存操作数所在的存储器地址。索引 寻址时·IX 和 IY 寄存器当作索引寄存器使用。当系统复位时 IX 和 IY 寄存器则会复位为 0。

#### 范例如下:

LD A, (IX) ; IX 为保存存储器地址之寄存器

LD A(IY+0x52) ; IY 为索引寄存器

IX(0x3A) ; IX 为通用寄存器 LD

在非多重中断操作时,核心寄存器功能可用来存储通用寄存器。在中断开始时,设定运算指令(如范例:LD RBS,1)·核心寄存器功能将可进行存储或转换。中断结束后,不需再重新执行运算指令, RETI 指令将会依 PSW 内容,自动将核心寄存器恢复主任务执行时的寄存器。

注:两个核心寄存器(BANK0 与 BANK1)都可使用。各核心寄存器由 8 位通用寄存器(W,A,B,C,D,E,H 与 L)和 16 位通用寄存器(IX 与 IY)所组成。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

范例:主任务使用 BANKO, 透过指令转换为 BANK1。

LD RBS, 1 ;Switches to the register bank BANK1 PINTxx:

Interrupt processing

;RETURN RETI

(Makes a return automatically to BANKO that was being used by the main task when the PSW is restored)

#### 3.2.3 程序状态字

程序状态字 PSW 位于地址 0x003F 的特殊功能寄存器 SFR 中。程序状态字 PSW 包含以下 6 个标帜位:

跳转状态标帜位 Jump Status Flag, JF

零标帜位 Zero Flag, ZF

进位标帜位 Carry Flag, CF

半进位标帜位 Half Carry Flag, HF

正负号标帜位 Sign Flag, SF

溢位标帜位 Overflow Flag, VF

除了通用的装载指令,专用指令亦可存取程序状态字组。下方表格列出条件跳转指令I例如"JJ cc, a"及"JRS cc,a" 指令)中标志位的状况。

| 条件代码 | 描述                                | 标志位状态              |

|------|-----------------------------------|--------------------|

| Т    | 1                                 | JF = 1             |

| F    | 0                                 | JF = 0             |

| Z    | Zero                              | ZF = 1             |

| NZ   | Not zero                          | ZF = 0             |

| CS   | Carry set                         | CF = 1             |

| CC   | Carry clear                       | CF = 0             |

| VS   | Overflow set                      | VF = 1             |

| VC   | Overflow clear                    | VF = 0             |

| М    | Minus                             | SF = 1             |

| Р    | Plus                              | SF = 0             |

| EQ   | Equal                             | ZF = 1             |

| NE   | Not equal                         | ZF = 0             |

| LT   | Unsigned less than                | CF = 1             |

| GE   | Unsigned greater than or equal to | CF = 0             |

| LE   | Unsigned less than or equal to    | $(CF ^ ZF) = 1$    |

| GT   | Unsigned greater than             | $(CF ^ ZF) = 0$    |

| SLT  | Signed less than                  | (SF ^ VF) = 1      |

| SGE  | Signed greater than or equal to   | (SF ^ VF) = 0      |

| SLE  | Signed less than or equal to      | ZF ^ (SF ^ VF) = 1 |

| SGT  | Signed greater than               | ZF ^ (SF ^ VF) = 0 |

表 3-3 条件代码表

iMQ Technology Inc.

No.: TDDS01-S7615-CN Name: SQ7615 中文产品规格书 Version: V1.9

# 3.2.4 堆栈指针(SP)

堆栈指针 SP 是一个 16 位寄存器,用来存放堆栈区中下一个可用空闲区域的地址。执行堆栈指令 PUSH、调用一个子程序或系统中断后,堆栈指针 SP 会减 1。执行弹出指令 POP、由子程序或中断返回前,堆栈指针 SP 加 1。 堆栈区中的地址次序安排是由高至低排列。

# 3.2.5 程序计数器(PC)

程序计数器 PC 是个 16 位寄存器,用来指示下一条要被执行的指令在程序存储器的地址。复位后,中央处理器 CPU 会将保存在矢量表中的复位矢量,装载进程序计数器 PC。CPU 接着读取并执行程序计数器所指示的地址所保存的指令。

Page: 41/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

# 3.3 寻址模式

产品线具备9种寻址模式,其中部分模式拥有不只一种类型,皆会干之后的章节分别描述。

| 寻址模式     | 类型数 |

|----------|-----|

| 寄存器间接寻址  | 7   |

| 直接寻址     | 2   |

| 寄存器寻址    | 1   |

| 立即寻址     | 1   |

| 相对寻址     | 2   |

| 绝对寻址     | 1   |

| 矢量寻址     | 1   |

| 直接位寻址    | 2   |

| 寄存器间接位寻址 | 1   |

| 总计       | 18  |

表 3-4 寻址模式及类型数量列表

## 3.3.1 寄存器间接寻址

寄存器间接寻址(HL), (DE), (IX), (IY)

16 位寄存器组 HL、DE、IX 及 IY 内容为有效地址。

范例:LD A,(HL)

寄存器间接加以 8 位偏移寻址(HL+d), (IX+d), (IY+d)

16 位寄存器 HL、IX、IY 内容,再加入符号扩展之 8 位偏移量 d 脚本,为有效地址。

范例:LD A,(HL+0x12) 寄存器索引寻址(HL+C)

寄存器 HL 内容,再加入符号扩展之 C 寄存器内容,为有效地址。

范例:LD A, (HL+C)

堆栈指针间接加以自动前置递增寻址(+SP)

堆栈指针 SP 递增内容为有效地址,而递增的 SP 不会影响到标志位。请注意,此寻址模式只能使用于指定源存 储器地址。

范例: LD A, (+SP)

**Page: 42/350**·不得变更内容及使用·汉芝电子保留随时修改本出版物内容之权益·恕不另行通相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

堆栈指针间接加以自动递减寻址(SP-)

SP 为有效地址,于数据处理后,SP 的内容会自动递减,此寻址模式只能使用于指定目标储存器地址。

范例:LD (SP-),A

堆栈指针间接加以 8 位偏移寻址(SP+d)

SP 内容,并于脚本中符号扩展 8 位偏移量 d,结合以上为有效地址。

范例: LD WA, (SP + 0xD6)

PC 相对寄存器间接寻址(PC+A)

程序计数器 PC 内容,再加入符号扩展之 A 寄存器内容,为有效地址,此寻址模式只能使用于指定源地址。

范例:LD A, (PC + A)

### 3.3.2 直接寻址

8 位直接寻址(x)

有效地址直接指定为 8 位脚本 x, 地址范围由 0x0000 至 0x00FF。

范例:LD A, (0x87)

16 位直接寻址(vw)

有效地址直接指定为 16 位脚本 vw · 地址储存范围由 0x0000 至 0xFFFF。

范例:LD A, (0x5678)

### 3.3.3 寄存器寻址(r 或 rr)

r或rr寄存器指令操作码之指定子可选定欲存取之寄存器。

范例:LD A,B

# 3.3.4 立即寻址(n 或 mn)

n 或 mn 寄存器指令操作码之指定子可选定欲存取之寄存器。

范例:LD A, 0x53

**Page: 43/350** · 不得变更内容及使用·汉

iMQ Technology Inc.

No.: TDDS01-S7615-CN Name: SQ7615 中文产品规格书 Version: V1.9

# 3.3.5.相对寻址

PC 相对加以 8 位偏移寻址

程序计数器 PC 内容·并于脚本中符号扩展 8 位偏移量 d·结合以上为有效地址。仅 JR 指令具有此寻址模式。

范例: JR \$ + 2 + 0x35

PC 相对加以 5 位偏移寻址

程序计数器 PC 内容·并于脚本中符号扩展 8 位偏移量 d·结合以上为有效地址。仅 JRS 指令具有此寻址模式。

范例: JRS \$ + 2 + 0x14

#### 3.3.6 绝对寻址

有效位置为 16 位指令操作码指定。

范例: JR 0x0F1A3

### 3.3.7 矢量寻址

4 位运算符乘 2 后加入矢量呼叫表上方地址,并指出 16 位跳转目标地址(矢量地址)。只有 CALLV 指令拥有此寻址模式。

#### 3.3.8 直接位尋址

寄存器位寻址

寄存器以及位指定子之指令操作码可于寄存器中选定一位位置,并对其值进行测试或是更换。

范例:SET A.3

存储器位寻址

存储器位寻址模式,脚本之位指定子选定于存储器中的位,其位所在位置由(HL)、(DE)、(IX)、(IY)、(HL+d)、(IX+d)、(IY+d)、(HL+C)、(+SP)、(SP+d)、(PC+A)、(x)或(vw)指出,并于此特定位进行位操作。 范例:SET (HL).1

Page: 44/350 本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

### 3.3.9 寄存器间接位寻址

于存储器位寻址模式·A寄存器中3个低阶位指定储存器中的任一位,其所在位置由(HL)、(DE)、(IX)、 (IY)、(HL+d)、(IX+d)、(IY+d)、(HL+C)、(+SP)、(SP+d)、(PC+A)、(x)或(vw)指出,并于此特定位进行 位操作。

范例: SET (HL).A

Page: 45/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

# 3.4 指令流水線

产品线核心使用三阶流水线执行指令动作,指令包含利用额外存取循环之存储器读存取

- 寄存器对寄存器运行

- 寄存器对存储器运行

- 存储器对寄存器运行

- 存储器对存储器运行

- 转跳

- 子过程调用及返回

- 软件中断(SWI)

### 3.4.1 寄存器对寄存器运行

此运行方式为三阶流水线,详如下列所述。

| 寄存器对寄存器运行之流水线作业 |                                         |  |

|-----------------|-----------------------------------------|--|

| 代码              | 阶段工作                                    |  |

| F               | 指令取出阶段,指令执行码会由编码存储器返回                   |  |

| D               | 指令译码阶段,指令被译码后传送至作业单元                    |  |

| Е               | 指令运行时间,执行单元会对指令进行作业,其结果会于执行循环结束后写回至寄存器堆 |  |

| F | D | Е |

|---|---|---|

|   | 1 |   |

### 3.4.2 寄存器对存储器运行

此运行方式为三阶流水线,详如下列所述。

| 寄存器对存 | 寄存器对存储器运行之流水线作业                                                   |  |  |

|-------|-------------------------------------------------------------------|--|--|

| 代码    | 阶段工作                                                              |  |  |

| F     | 指令取出阶段,指令执行码会由编码存储器返回                                             |  |  |

| D     | 指令译码阶段,指令被译码后传送至作业单元                                              |  |  |

| Е     | 运行时间,执行单元会对指令进行作业,其结果于执行循环结束后写回储存数据缓冲器。<br>缓冲器内的数据会于下一个循环时传送至总线接口 |  |  |

|--|

iMQ Technology Inc.

No.: TDDS01-S7615-CN Name: SQ7615 中文产品规格书 Version: V1.9

### 3.4.3 存储器对寄存器运行

此类型的操作具存储器读取,因此有另一个存储器存取循环。

| 存储器对寄存器运行之流水线作业 |                                         |  |

|-----------------|-----------------------------------------|--|

| 代码              | 阶段工作                                    |  |

| F               | 指令取出阶段,指令执行码会由编码存储器返回                   |  |

| D               | 指令译码阶段,指令被译码后传送至作业单元                    |  |

| М               | 存储器存取循环,产生地址并传送至数据总线接口                  |  |

| F               | 运行时间,装载的数据会返回且执行单元进行作业,其结果会于执行循环结束后写回寄存 |  |

|                 | 器堆                                      |  |

| F D I | M E |

|-------|-----|

|-------|-----|

# 3.4.4 存储器对存储器运行

此类型的操作在存储器写循环后进行存储器读取,因此具另一个存储器存取循环。

| 存储器对存储器运行之流水线作业 |                                           |  |

|-----------------|-------------------------------------------|--|

| 代码              | 阶段工作                                      |  |

| F               | 指令取出阶段·指令执行码会由编码储存器返回                     |  |

| D               | 指令译码阶段·指令被译码后传送至作业单元                      |  |

| М               | 储存器存取循环,产生地址并传送至数据总线接口                    |  |

| F               | 运行时间, 装载的数据会返回且执行单元进行作业, 其结果会于执行循环结束后写回寄存 |  |

| E               | 器堆。其缓冲器内的数据会于下一个循环时传送至总线接口                |  |

| F | D | М | Е |

|---|---|---|---|

|---|---|---|---|

Page: 47/350本出版物内容版权为汉芝电子所有,非经汉芝电子书面同意,不得变更内容及使用,汉芝电子保留随时修改本出版物内容之权益,恕不另行通知。购买汉芝电子产品前,请联络汉芝电子取得最新版本的相关技术文件。汉芝电子产品并非设计应用于直接或间接地导致生命损害、死亡、人身伤害之相关领域,汉芝电子在此排除任何使用于上述领域所产生之损害赔偿责任。

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

# 3.4.5 跳转

两种跳转类型:

| 跳转类型 1 |                                                                                      | 跳转类型 2  |                                                                         |

|--------|--------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------|

| 寻址模式   | 操作码                                                                                  | 寻址模式    | 操作码                                                                     |

| 寄存器寻址  | JP gg                                                                                | 寄存器间接寻址 | JP (src*) *src: DE, HL, IX, IY, IX+d, IY+d, SP+d, HL+d, HL+C, +SP, PC+A |

| 立即寻址   | JP mn                                                                                | 直接寻址    | JP (src*)<br>*src: x, vw                                                |

| 相对寻址   | 1) PC 相对加以 8 位偏移寻址<br>JR T,\$+2+d, etc.<br>2) PC 相对加以 5 位偏移寻址<br>JRS T, \$+2+d, etc. |         |                                                                         |

| 绝对寻址   | JP 0x0F1A3                                                                           |         |                                                                         |

#### 类型1流水线:

此种转跳类型有三阶流水线作业,详如下列所述。

| 跳转类型 1 之流水线作业 |                                       |  |  |  |

|---------------|---------------------------------------|--|--|--|

| 代码            | 阶段工作                                  |  |  |  |

| F             | 指令取出阶段,指令执行码会由编码存储器返回                 |  |  |  |

| D             | 指令译码阶段,指令被译码后传送至作业单元                  |  |  |  |

| Е             | 运行时间,执行单元会对指令进行作业,其结果会于执行循环结束后写回至寄存器堆 |  |  |  |

| F | D | Е |

|---|---|---|

|   |   |   |

### 类型 2 流水线:

此种跳转类型有五阶流水线作业,详如下列所述。

|     | 跳转类型 2 之流水线作业             |  |  |

|-----|---------------------------|--|--|

| 代码  | 阶段工作                      |  |  |

| F   | 指令取出阶段,指令执行码会由编码存储器返回     |  |  |

| D   | 指令译码阶段·指令被译码后传送至作业单元      |  |  |

| Е   | 运行时间·数据单元产生间接地址后传送至数据总线接口 |  |  |

| E+1 | 转跳目标地址返回并储存于装载数据缓冲器       |  |  |

| E+2 | 指令取出地址产生                  |  |  |

| F D E E+1 E+2 |

|---------------|

|---------------|

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

# 3.4.6 子过程调用及返回

两种呼叫类型:

| 1     | 呼叫类型 1       | 呼叫类型 2 |     |  |

|-------|--------------|--------|-----|--|

| 寻址模式  | 操作码          | 寻址模式   | 操作码 |  |

| 寄存器寻址 | -            | 寄存器寻址  | -   |  |

| 立即寻址  | -            | 直接寻址   | -   |  |

| 绝对寻址  | CALL 0x0F1A3 |        |     |  |

| 矢量寻址  | CALLV 0x9    |        |     |  |

#### 类型 1 流水线

此种呼叫类型有三阶流水线作业,详如下列所述。

| 呼叫类型 1 之流水线作业 |                                       |  |  |  |

|---------------|---------------------------------------|--|--|--|

| 代码            | 阶段工作                                  |  |  |  |

| F             | 指令取出阶段,指令执行码会由编码存储器返回                 |  |  |  |

| D             | 指令译码阶段,指令被译码后传送至作业单元                  |  |  |  |

| Е             | 运行时间,执行单元会对指令进行作业,其结果会于执行循环结束后写回至寄存器堆 |  |  |  |

### 类型 2 流水线

此种跳转类型有五阶流水线作业,详如下列所述。

|     | 呼叫类型 2 之流水线作业             |  |  |

|-----|---------------------------|--|--|

| 代码  | 阶段工作                      |  |  |

| F   | 指令取出阶段,指令执行码会由编码存储器返回     |  |  |

| D   | 指令译码阶段,指令被译码后传送至作业单元      |  |  |

| Е   | 运行时间,数据单元产生间接地址后传送至数据总线接口 |  |  |

| E+1 | 转跳目标地址返回并储存于装载数据缓冲器       |  |  |

| E+2 | 指令取出地址产生                  |  |  |

| F | D | Е | E+1 | E+2 |

|---|---|---|-----|-----|

|---|---|---|-----|-----|

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

# 3.4.7 软件中断(SWI)

软件中断指令有六阶流水线作业,详如下列所述。

| 软件中断之流水线作业 |                                           |  |

|------------|-------------------------------------------|--|

| 代码         | 阶段工作                                      |  |

| F          | 指令取出阶段·指令执行码会由编码存储器返回                     |  |

| D          | 指令译码阶段·指令被译码后传送至作业单元                      |  |

| Е          | 运行时间,执行 SWI 指令,指令单元接收中断矢量地址同时产生指令取出地址。在此循 |  |

|            | 环·PSW 推至堆栈区                               |  |

| F+1        | 中断矢量返回且将指令缓冲器视为转跳指令输入。在此循环,下一个操作码地址被推至堆   |  |

| L'1        | 栈区                                        |  |

| E+2        | 译码跳转目标地址                                  |  |

| E+3        | 指令单元矢量传至 SWI 中断程序                         |  |

| F D | Е | E+1 | E+2 | E+3 |

|-----|---|-----|-----|-----|

|-----|---|-----|-----|-----|

iMQ Technology Inc.

Name: SQ7615 中文产品规格书 No.: TDDS01-S7615-CN Version: V1.9

# 3.5 指令集总结

指令集可分成六个群族如下,并于各个节说明;此章节亦会描述指令助记符以及执行循环

数据传送及交换指令

算数逻辑单元(ALU)指令

位移/旋转及半字节操作指令

位及标志操作指令

转跳指令

呼叫、返回、软件中断以及无操作指令

# 3.5.1 数据传送及交换指令

| 运算动作     | 描述                                    | 汇编语言          | 指令周期 |